# nature communications

**Article**

https://doi.org/10.1038/s41467-024-50185-4

# High-density vertical sidewall MoS<sub>2</sub> transistors through T-shape vertical lamination

Received: 26 December 2023

Accepted: 3 July 2024

Published online: 10 July 2024

Quanyang Tao<sup>1,2,4</sup>, Ruixia Wu<sup>1,3,4</sup>, Xuming Zou  $^1 \boxtimes$ , Yang Chen<sup>1</sup>, Wanying Li<sup>1</sup>, Zheyi Lu<sup>1</sup>, Likuan Ma<sup>1</sup>, Lingan Kong  $^1$ , Donglin Lu<sup>1</sup>, Xiaokun Yang<sup>1</sup>, Wenjing Song<sup>1</sup>, Wei Li<sup>3</sup>, Liting Liu<sup>1</sup>, Shuimei Ding<sup>1</sup>, Xiao Liu<sup>1</sup>, Xidong Duan  $^3$ , Lei Liao  $^2 \boxtimes$  & Yuan Liu  $^1$

Vertical transistors, in which the source and drain are aligned vertically and the current flow is normal to the wafer surface, have attracted considerable attention recently. However, the realization of high-density vertical transistors is challenging, and could be largely attributed to the incompatibility between vertical structures and conventional lateral fabrication processes. Here we report a T-shape lamination approach for realizing high-density vertical sidewall transistors, where lateral transistors could be pre-fabricated on planar substrates first and then laminated onto vertical substrates using T-shape stamps, hence overcoming the incompatibility between planar processes and vertical structures. Based on this technique, we vertically stacked 60 MoS<sub>2</sub> transistors within a small vertical footprint, corresponding to a device density over 10<sup>8</sup> cm<sup>-2</sup>. Furthermore, we demonstrate two approaches for scalable fabrication of vertical sidewall transistor arrays, including simultaneous lamination onto multiple vertical substrates, as well as on the same vertical substrate using multi-cycle layer-by-layer laminations.

Field-effect transistors (FETs) represent the fundamental building blocks for modern computer processors. Today's dominant device architecture is lateral-transport FET (ref. 1,2), which layers transistors along a wafer's surface. By making the lateral size of transistors smaller and smaller through advanced lithography, more transistors can be integrated into a single chip with much improved integration density<sup>3</sup>. Today, as transistor pitch size (lateral distance between two neighbor transistors) enters the sub-50-nm regime with increasing technical challenges<sup>4</sup>, the exploration of alternative device geometries is ever more important for further increasing the transistor density and extending Moore's law. Vertical-transport FETs (VFETs)<sup>5-9</sup>, on the other hand, layer transistors perpendicularly to the wafer plane and direct

the current flow vertically to the wafer surface. Within this device structure, each device is stacked on top of another and does not consume additional chip footprint beyond what is needed for a single device placed at the bottom<sup>10–13</sup>, opening up another dimension for high-density integrated circuits.

However, fabricating vertical transistors is technologically challenging, and could be largely attributed to the incompatibility with conventional lateral-based fabrication processes. For example, to fabricate a single vertical transistor, the bottom source electrode layer needs to be created first, followed by the deposition of the channel layer and the drain electrode layer. To stack multiple devices within the vertical direction, these processes have to be repeated, leading to

<sup>1</sup>Key Laboratory for Micro-Nano Optoelectronic Devices of Ministry of Education, School of Physics and Electronics, Hunan University, Changsha, China. <sup>2</sup>Changsha Semiconductor Technology and Application Innovation Research Institute, College of Semiconductors (College of Integrated Circuits), Hunan University, Changsha, China. <sup>3</sup>State Key Laboratory for Chemo/Biosensing and Chemometrics, College of Chemistry and Chemical Engineering, Hunan University, Changsha, China. <sup>4</sup>These authors contributed equally: Quanyang Tao, Ruixia Wu. ⊠e-mail: zouxuming@hnu.edu.cn; liaolei@whu.edu.cn; yuanliuhnu@hnu.edu.cn

complex fabrication processes with low throughput. Hence, the stateof-the-art vertical transistor is largely limited to the demonstration of a few device layers in vertical direction 5,14-18, limiting the achievement of high-density devices. This is in great contrast to the planar integrated circuit techniques based on advanced lithography and deposition processes, where large amounts of lateral devices (over millions or billions) could be batch-fabricated in parallel. These differences originate from the fact that conventional lateral processes are top-down approaches involving physical particles such as photons (in lithography), reactive ions (in etching), or physical/chemical vapors (in deposition), which can only generate multiple structures within the wafer plane. Creating scalable structures vertically (perpendicular to the wafer plane) using these techniques is difficult since these physical particles (photons, ions, vapors) can not be applied to the vertical substrate. Therefore, developing a new process that can generate multiple structures vertically is critical for the realization of highdensity VFETs.

In this work, we report an alternative approach to fabricating multiple vertical sidewall transistors simultaneously. Lateral transistors could be pre-fabricated on a planar substrate using conventional batch processes, further dry-released, and laminated onto the vertical substrate through a custom-designed T-shape stamp, hence overcoming the incompatibility between planar processes and vertical structures. Importantly, owing to the low strain induced during the dry-lamination process, the transistors could conformally contact with

the vertical substrate without damage or degradation, leading to high-performance vertical transistors with low device-to-device variation. Based on this technique, we vertically stacked 60 MoS $_2$  transistors within a small footprint of 0.035  $\mu m^2$ , corresponding to a theoretical device density of  $1.7\times10^{11}\,\text{cm}^{-2}$  and  $2.4\times10^{8}\,\text{cm}^{-2}$ , depending on the definition of device area. Finally, we demonstrate two approaches for scalable fabrication of vertical sidewall transistor arrays, including simultaneous lamination onto multiple vertical substrates, as well as multi-cycle layer-by-layer laminations on the same vertical substrate. Our results offer an alternative route for the vertical electronics and high-density transistors.

# **Results**

#### **Vertical lamination processes using T-shape stamp**

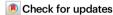

Figure 1a–e schematically illustrates the vertical lamination processes of two-dimensional  $MoS_2$  transistors. First of all, lateral  $MoS_2$  transistors are pre-fabricated on a silicon sacrifice wafer, using conventional planar processes of lithography and thermal deposition. The whole device layer (both  $MoS_2$  channel and Au electrodes) could be mechanically released from the sacrificial substrate with the assistant of PMMA (polymethyl methacrylate) capping layer using our previously developed method <sup>19–21</sup> (detailed in "Methods"), as shown in Fig. 1a. We note the dry releasing approach is essential to avoid the involvement of solutions, hence maintaining the intrinsic properties of  $MoS_2$  channel and metal contact. Next, the vertical

**Fig. 1** | **Vertical lamination processes and characterization of MoS<sub>2</sub> based vertical sidewall transistors. a–e** Schematics and the corresponding optical images of the vertical lamination processes with 5 steps: planar MoS<sub>2</sub> transistors prefabricated on a sacrificial substrate (**a**), fabrication of vertical silicon trench through etching (**b**), dry-transfer of MoS<sub>2</sub> transistors with the polymethyl methacrylate (PMMA) gap on top of Si trench (**c**), T-shape polydimethylsiloxane (PDMS) stamp laminated and pushed into the trench (**d**), and MoS<sub>2</sub> vertical transistors after

lamination (e). **f** Scanning electron microscopy (SEM) image of the fabricated  $MoS_2$  vertical transistors on vertical substrate. **g-i** Cross-sectional SEM image (**g**) and scanning transmission electron microscopy (STEM) images (**h**, **i**) of the vertical transistors, indicating the optimized interface after vertical lamination. Scale bars are  $10 \, \mu m$  for panel **a**, **c**, **e**,  $20 \, \mu m$  for panel **b**, **d**. S, source; D, drain.

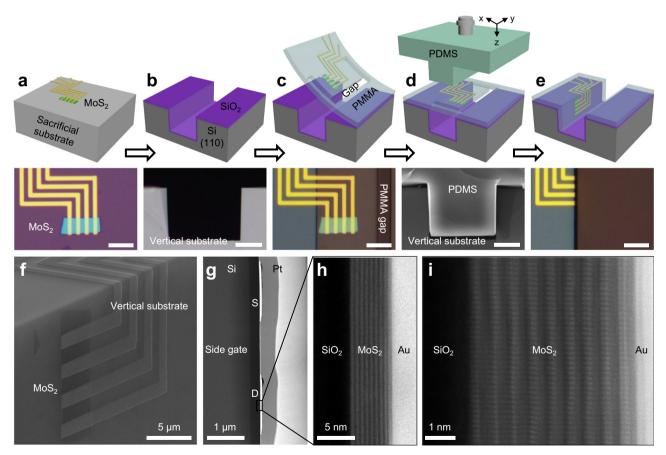

**Fig. 2** | **Electrical characterizations of MoS**<sub>2</sub> **transistors. a**, **b** Transfer characteristics of the 11 parallel MoS<sub>2</sub> transistors on the pre-fabricated lateral substrate (a) as well as after lamination on the vertical substrate (b). Insets are the corresponding device images. **c** Comparison of the mobilities and on/off ratios for lateral and vertical transistors, where comparable electrical properties and low device-to-device variations are observed. **d** Circuit diagram (upper) and optical image of pre-fabricated lateral NMOS inverter composed of two MoS<sub>2</sub> transistors in series. The

black, white, and red dashed boxes are graphene,  $MoS_2$ , and BN, respectively.  $\mathbf e$  The voltage transfer characteristic (black line) and voltage gain (red line) of the vertical inverter at supply voltage of  $2\,V$ .  $\mathbf f$  Retention performance of the vertical floating gate memory. Insets are the schematics of the inverter ( $\mathbf e$ ) and memory ( $\mathbf f$ ), respectively.  $V_{gs}$ , gate-source voltage;  $V_{ds}$ , drain-source voltage;  $I_{ds}$ , drain-source current; GND, ground;  $V_{in}$ , input voltage;  $V_{out}$ , output voltage;  $V_{dd}$ , supply voltage.

substrate is prepared by wet etching of Si substrate  $^{22-24}$  ("Methods"), creating a deep Si sidewall (-  $40\,\mu m$  depth), as shown in Fig. 1b. Furthermore, the released device layer is laminated on top of the Si vertical substrate (covered by  $300\,nm$  thick vertical  $SiO_2$ ) using dryalignment transfer process, as schematically illustrated in Fig. 1c and Supplementary Fig. 1. In conventional lamination processes, the laminated device layer can only form good contact with the bottom flat surface, the integration of the devices on the deep vertical substrate could lead to the suspension of device layer on the silicon sidewall, as shown in Fig. 1c. To overcome this challenge, a T-shape PDMS (polydimethylsiloxane) stamp is designed (Methods), where the suspended  $MoS_2$  transistors could be precisely pushed onto the vertical substrate, leading to the intimate contact between the device layer and the vertical substrate (Fig. 1d, e).

We note our T-shape vertical lamination process is unique to achieve vertically stacked transistors, owing to two factors. First of all, the T-shape PDMS stamp is fabricated using the same silicon vertical trench as the mold (Methods), hence, the stamp has the exact same structure to fit the deep silicon trench, as shown in Fig. 1d. When mechanically moving the micro-sized T-shape stamp into the trench, it could push the device layer onto the vertical sidewall to form intimate contact between the device layer and the vertical substate (Fig. 1e). This can be confirmed in the scanning electron microscopy (SEM) image as well as the scanning transmission electron microscopy (STEM) images (Fig. 1f-i), where the device layer is closely contacted with the vertical substrate without any air bubbles. Second, both the device releasing process and the vertical lamination process are based on dry processes without solvents and mechanical stress. In contrast, the conventional wet-transfer process<sup>25</sup> on the non-flat substrate (or vertical substrate) is based on capillary force between the substrate during the solution evaporation, leading to a large stretching force and the distortion of the device layer, as shown in our control experiment in Supplementary Fig. 2.

#### Electrical properties of vertical sidewall MoS<sub>2</sub> transistors

To demonstrate the robustness of our T-shape vertical lamination technique, we have measured and compared the electrical properties of the MoS<sub>2</sub> transistors on both lateral substrate and vertical substrate. As shown in Fig. 2a, a lateral MoS<sub>2</sub> transistor array is fabricated on a conventional flat substate, where highly doped Si substrate is used as the back gate, 300 nm thick SiO<sub>2</sub> is used as the gate dielectric, Au (50 nm thick) is used as the source/drain electrodes, respectively. The electrical measurements of the as-fabricated lateral devices were conducted at room temperature in a vacuum probe station (10<sup>-4</sup> Torr). In general, n-type transfer behaviors (Fig. 2a) are observed with an onoff ratio over 106, demonstrating decent electrical properties and consistent with previous literatures<sup>20,26,27</sup>. In particular, the 11 parallel devices demonstrate low device-to-device variation in terms of onstate current (<10%), indicating the optimized device conditions using our fabrication techniques. After electrical measurements, these planar transistors are released from flat back-gate substrate and further laminated on the vertical substrate using our T-shape lamination process described in Fig. 1. We note the sidewall of highly doped silicon is also covered with 300 nm thick SiO2, hence, global side gate with identical dielectric conditions is achieved. As shown in Fig. 2b, the vertical transistors demonstrate similar n-type switching behaviors, indicating the T-shape lamination process won't alter the intrinsic properties of the MoS<sub>2</sub> channel and contact conditions. Figure 2c summarizes the on-off ratios and field effect mobilities of these devices on both lateral and vertical substrates, where similar electrical properties are observed, confirming the device layer is conformally contacted to the vertical side gate with efficient gate modulation. To further investigate the device uniformity, we have fabricated 60 planar and vertical transistors, and statistically analyzed their transfer curves. As shown in Supplementary Fig. 3, their key electrical properties demonstrate low device-to-device variations, further confirming the transistors remain free from damage or degradation after vertical

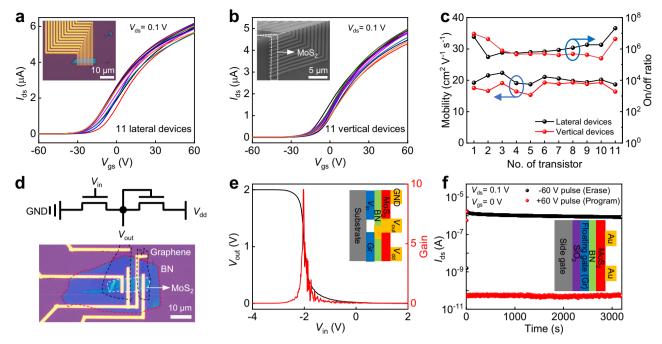

Fig. 3 | Scalable fabrication of vertical sidewall transistors. a 60 lateral monolayer MoS $_2$  transistor with 0.15  $\mu m$  channel length (*L*) and 0.5  $\mu m$  channel width (*W*). Inset is the optical image of lateral MoS $_2$  transistors. b SEM image of vertical MoS $_2$  transistors. Inset is the corresponding cross-sectional schematic. The white dashed boxes are MoS $_2$  in panels a, b. c Schematic of the definition of device area in the density calculation. d Optical image of vertical device arrays with a pitch size of

420  $\mu m$  in the *x*-direction and 90  $\mu m$  in the *y*-direction. **e** Zoomed-in optical image of vertical device arrays. **f** Cross-sectional image of T-shape PDMS stamp array, inset is the cross-sectional SEM image of one T-shape PDMS stamp. The white arrows point to T-shape PDMS stamps. **g** SEM images of vertical devices at different locations (marked in (**d**)).

lamination. Besides global side-gate devices, we could also fabricate separated gates for vertical  $MoS_2$  devices using  $10 \text{ nm Al}_2O_3$  as the dielectric, as shown in Supplementary Fig. 4.

Furthermore, our T-shape vertical lamination technique could be well extended to more complex device structures. To demonstrate this, a MoS<sub>2</sub>-based NMOS inverter is pre-fabricated by connecting two transistors in series, as schematically illustrated in Fig. 2d. After integrating the whole device layer on the vertical substrate (Fig. 2e, inset and Supplementary Fig. 5a), the inverter demonstrates sharp output voltage ( $V_{\text{out}}$ ) transition as a function of input voltage ( $V_{\text{in}}$ ), yielding a voltage gain (defined as  $|dV_{out}/dV_{in}|$ ) of 10 at supply voltage ( $V_{dd}$ ) of 2 V (Fig. 2e). Beyond logic devices, our technique could also be applied to fabricated other vertical devices such as memory. For example, a fourlayer van der Waals heterostructure (graphene/BN/MoS<sub>2</sub>/Au) memory<sup>28</sup> could also be pre-fabricated on a lateral substrate, where the graphene, BN, MoS<sub>2</sub>, and Au are used as a floating gate, tunneling dielectric, semiconductor channel, and metal contact, respectively. After laminating the memory using a T-shape PDMS stamp, the vertical device demonstrates a large memory window using a side control gate,

and the program and erase states show a significant program/erase (P/E) current ratio exceeding  $10^4$  (Supplementary Fig. 5b). Importantly, the large P/E ratio remains after more than  $3000\,\mathrm{s}$  measurement (Fig. 2f), indicating the high durability of our vertical memory.

# Scalable fabrication of high-density transistors

Achieving high integration density is the primary motivation for stacking vertical transistors, where multiple devices could be stacked together in the vertical direction and do not consume additional chip footprint beyond what is needed for a single device placed at the bottom. To achieve high-density vertical devices, we have pre-fabricated 60 short channel MoS $_2$  transistors on a sacrificial planar wafer, and the channel length, contact length, and channel width are 0.15, 0.15 and 0.5 µm, respectively, as shown in Fig. 3a. Furthermore, we have laminated these short-channel devices on the vertical substrate using our vertical lamination technique, where the side gate is 30 nm thick Cr/Au, the side dielectric is 10 nm thick Al $_2$ O $_3$ , the monolayer MoS $_2$  is 0.7 nm, and the source/drain electrodes are 30 nm thick Au, as shown in Fig. 3b. The electrical

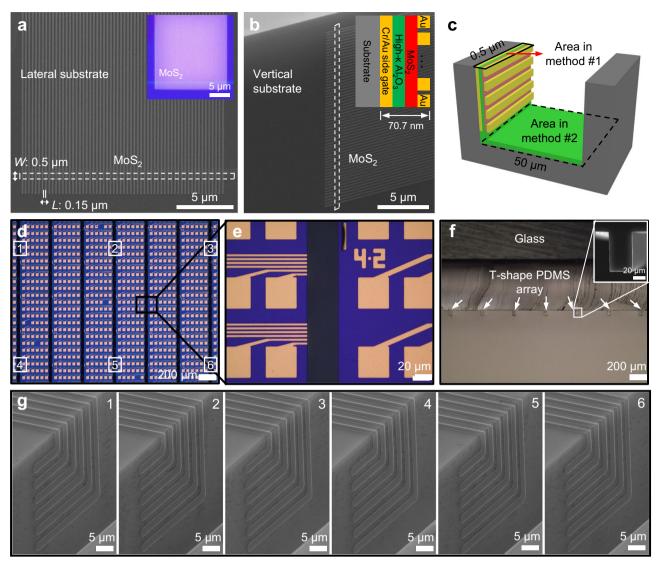

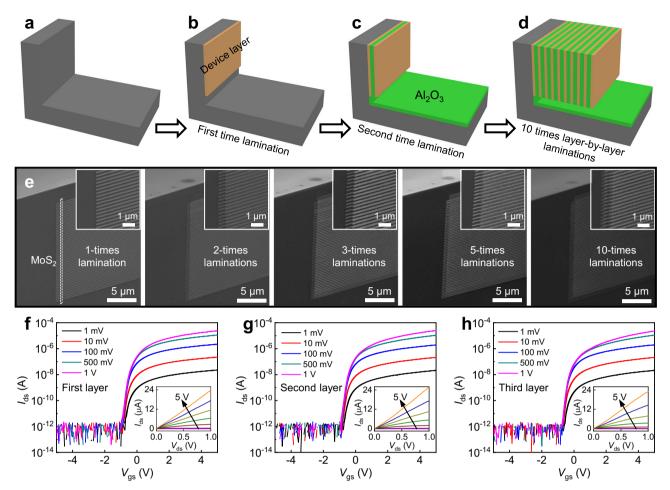

Fig. 4 | Layer-by-layer vertical integrations of high-density vertical devices. a-d Schematics of the 10 times layer-by-layer vertical laminations of vertical transistors on the same sidewall. e The corresponding SEM images of vertical devices. The channel length and contact length of all devices are fixed at 0.15  $\mu$ m, the channel width is 0.2  $\mu$ m, the source/drain electrodes are 20 nm thick Au, and the interlayer dielectric (between two adjacent vertical layers) is 10 nm thick Al<sub>2</sub>O<sub>3</sub>.

Insets are the corresponding zoomed-in SEM images of vertical devices. f-h Transfer curves and output curves (inset) of the first-layer (f), second-layer (g), and third-layer (h) MoS<sub>2</sub> transistor, demonstrating consistent electrical properties. For output curves, various gate voltages from -5 V to 5 V are applied with a step of 1 V.

measurements of short-channel vertical devices are shown in Supplementary Fig. 6, exhibiting on-state current of up to  $400 \,\mu\text{A}/\mu\text{m}$ , small subthreshold swing of  $110 \,\text{mV}/\text{dec}$  and high on-off ratio of  $10^\circ$ .

The device density could be further calculated using the device number divided by the total device area. Here, the device number is 60, and the device area is defined using two different methods. In the first method (method #1), the total device area is the planar region of one device, which is  $\sim 0.035 \,\mu\text{m}^2 \,(70.7 \,\text{nm} \times 0.5 \,\mu\text{m})$ including all active components (gate electrode, dielectric layer, MoS<sub>2</sub> channel, and source/drain electrodes), as schematically illustrated in Fig. 3c. Therefore, the highest density of  $1.7 \times 10^{11}$  cm<sup>-2</sup> could be calculated by using 60/(0.035 µm<sup>2</sup>). We note such high device density only represents the upper limit of our current fabrication process and cannot be realized in wafer size, because we ignore the larger trench area and vertical substrate area that are necessary for device fabrication. In the meantime, this theoretical integration density could be further increased by reducing the pitch size of the lateral device (using higher lithography resolution) or increasing the sidewall height (using deeper etching), as shown in Supplementary Fig. 7. On the other hand, in the second method (method #2), the device area is calculated by the total trench area, as schematically shown in Fig. 3c. Using this method, 60 vertical devices are located in a larger trench with area of 25 µm<sup>2</sup>  $(50 \,\mu\text{m} \times 0.5 \,\mu\text{m})$ , leading to a device density of  $2.4 \times 10^8 \,\text{cm}^{-2}$ .

Furthermore, the high-density vertical devices could be scalable and realized by integrating devices onto multiple vertical sidewalls. To achieve this, we have fabricated device arrays with a pitch size of 420  $\mu m$  in the x-direction and 90  $\mu m$  in the y-direction (distance between two adjacent arrays), as shown in Fig. 3d, e. We note the array pitch size could be further reduced once the transistors are interconnected (without a large area of measurement pads). Next, the T-shape PDMS array is also fabricated with the same spacing, as shown in Fig. 3f. Finally, all transistors could be vertically laminated into the different trenches simultaneously with the assistance of the T-shape PDMS array (Fig. 3g), highlighting the potential of scalable vertical lamination.

#### Layer-by-layer T-shape vertical integration

Due to the exact same structure between the T-shape PDMS stamp and the silicon sidewall, the vertical lamination process is highly robust and reproducible and could be repeated several times to realize layer-by-layer vertical lamination without consuming additional space or fabricating additional sidewalls. As shown in Fig. 4a, b, the first layer  $MoS_2$  transistor array is vertically integrated onto the sidewall using the method described above. Next, atomic layer deposition is conducted to uniformly deposit the vertical interlayer dielectric. Afterwards, the second layer  $MoS_2$  transistor array is further integrated onto the same sidewall using a T-shape lamination process, as illustrated in Fig. 4c.

This layer-by-layer vertical lamination could be further repeated for realizing high-density devices over a larger area. As a proof-of-concept demonstration, we have laminated 10 device layers successfully on the same vertical sidewall, as shown in Fig. 4d, e and Supplementary Fig. 8. With the assistance of layer-by-layer lamination, the device density is correspondingly increased using method #2, but would still remain the same if using method #1 for calculation. Since the trench structure could be batch-fabricated (as demonstrated in Fig. 3d), the realization of such device density over a large scale would be an interesting topic for further investigation.

Electrical characterizations are further conducted to examine the device qualities and the impact of layer-by-layer integration. The transfer curves and output curves of the MoS<sub>2</sub> transistors of three different layers are shown in Fig. 4f–h, and the corresponding device images are shown in Supplementary Fig. 9a–d. The devices in different vertical layers exhibit similar device performances (e.g., threshold voltage, on-state current), indicating our vertical lamination process won't alter the intrinsic properties of the bottom layer. Furthermore, to avoid electrical coupling, PMMA interlayer dielectric (-1 μm thick) is also laminated between each layer. As shown in Supplementary Fig. 9e–g, the device in the second layer exhibits consistent electrical performances with different gate voltages from the first layer, and its threshold voltage remains stable under various back gate voltages, indicating the low-κ PMMA layer could effectively reduce the interlayer electrical coupling.

#### Discussion

In summary, we demonstrate a simple method to fabricate highdensity vertical sidewall transistors by transferring pre-fabricated lateral transistors onto vertical substrates. Utilizing a custom-designed Tshape PDMS stamp lamination, the pre-fabricated transistors could conformally contact to the vertical substrate without damage or degradation, as verified by SEM, STEM, and electrical characterizations, hence overcoming the incompatibility between planar processes and vertical structures. With this technique, we have achieved a theoretical transistor density of up to 1.7 × 10<sup>11</sup> cm<sup>-2</sup> in the limited area of 0.035 µm<sup>2</sup>. Furthermore, we also provide two feasible approaches for the scalable fabrication of vertical sidewall transistor arrays, including simultaneous lamination onto multiple vertical substrates, as well as layer-by-layer laminations on the same vertical substrate. Our study realizes the stacking of multiple vertical transistors in a simple approach, opening up a new dimension for high-density integrated circuits.

#### Methods

#### Vertical substrates fabrication

Cr/Au (20/40 nm) patterns (width 500  $\mu$ m and spacing 50  $\mu$ m) are first fabricated on a Si (110) wafer through standard photolithography and high vacuum electron-beam evaporation. Next, the silicon is etched (using the Cr/Au layer as a mask) within 30% KOH solution at 100 °C for a few minutes to create deep vertical Si trenches. After the Cr/Au mask is removed by the  $I_2$ /KI and chromium solution, thermal oxidation is performed in a tube furnace under  $O_2$  flow (150 sccm) at 1000 °C to obtain  $SiO_2$  with a desired thickness, which is further measured and confirmed by focused ion beam and SEM characterization. We note that as the trench width decreases to below 3  $\mu$ m, the T-shape PDMS stamp will be difficult to fit into the trench due to its poor visibility (high transparency) and low alignment accuracy (-1  $\mu$ m), limiting the yield of the vertical lamination process.

#### T-shape PDMS stamp preparation

A Si trench is treated by hexamethyldisilazane (HMDS) first to facilitate the subsequent release of the PDMS stamp from the Si mold (width 50  $\mu$ m, as described in previous section). Next, PDMS elastomer (Sylgard 184, Dow Corning) is casted onto the Si mold to a thickness of 2 mm,

followed by baking at  $60\,^{\circ}\text{C}$  for 12 hours and then peeling off from the mold to create the T-shape PDMS stamp with the same structure as the Si mold.

#### Dry integration progress for sidewall device

First, a few-layer MoS<sub>2</sub> is mechanically exfoliated onto SiO<sub>2</sub> (300 nm) substrate, PMMA is spin-coated onto the substrate, and electrodes are defined via standard electron-beam lithography, followed by the deposition of 50 nm Au as contact electrodes (Supplementary Fig. 1a). Since the electrodes pass through vertical corners during vertical lamination process, it is necessary to choose the metal with good ductility, such as Au, Ag, Pt. Then, the wafer is functionalized by an HMDS layer in a sealed chamber at 80 °C for 10 mins and covered by a PMMA layer (~1 µm thick, Supplementary Fig. 1b). A PMMA gap is created by electron-beam lithography and development processes to release stress during the vertical lamination process (Supplementary Fig. 1c). The device layer can be picked up from the substrate by a flat PDMS stamp, transferred and released on top of the trench (Supplementary Fig. 1d-f). Subsequently, another T-shape PDMS stamp is pushed and fully embedded into the trench, thus the devices are pushed onto the vertical sidewall to form intimate contact between the device layer and the vertical substate (Supplementary Fig. 1g-i). For SEM characterizations, chloroform can be used to remove the PMMA layer (Supplementary Fig. 1j). To further reduce the wafer surface usage, we could laminate more devices with total length longer than the trench width. As shown in Supplementary Fig. 10, a 40 µm wide device array can still be pushed through a 27 µm long window.

## Materials characterizations and electrical measurements

SEM images are collected by TESCAN MIRA3 and VEGA3 at 20 kV, and cross-sectional STEM characterizations are performed using Thermo Scientific Themis Z 3.2, operating at 300 kV. To obtain better performance, the devices are annealed at 200 °C for two hours under an argon atmosphere<sup>29</sup>. Afterwards, electrical measurements are carried out in a probe station (Lakeshore, PS-100) at room temperature in a vacuum using an Agilent B1500A semiconductor analyzer. Note that the Si substrate is disconnected without applying voltage in the multilayer measurement. In addition, because the Si substrate is covered with a thick dielectric layer, electrical performance for each layer is largely unaffected by the Si substrate.

## Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

# References

- Hisamoto, D. et al. A folded-channel MOSFET for deep-sub-tenth micron era. In 1998 IEEE International Electron Devices Meeting (IEDM) 1032–1034 (IEEE, 1998).

- Huang, X. et al. Sub 50-nm FinFET: PMOS. In 1999 IEEE International Electron Devices Meeting (IEDM) 67–70 (IEEE, 1999).

- Waldrop, M. M. The chips are down for Moore's law. Nature 530, 144–147 (2016).

- International Roadmap for Devices and Systems (IRDS™) 2021 Edition (IEEE). https://irds.ieee.org/editions/2021 (2021).

- Jagannathan, H. et al. Vertical-transport nanosheet technology for CMOS scaling beyond lateral-transport devices. In 2021 IEEE International Electron Devices Meeting (IEDM) 26.21.21–26.21.24 (IEEE, 2021).

- Moers, J. Turning the world vertical: MOSFETs with current flow perpendicular to the wafer surface. Appl. Phys. A 87, 531–537 (2007).

- Chan, I. & Nathan, A. Amorphous silicon thin-film transistors with 90° vertical nanoscale channel. Appl. Phys. Lett. 86, 253501 (2005).

- Johnston, D. E., Yager, K. G., Nam, C. Y., Ocko, B. M. & Black, C. T. One-volt operation of high-current vertical channel polymer semiconductor field-effect transistors. *Nano Lett.* 12, 4181–4186 (2012).

- McClellan, C. J., Yu, A. C., Wang, C.-H., Wong, H. S. P. & Pop, E. Vertical sidewall MoS<sub>2</sub> growth and transistors. In 2019 Device Research Conference (DRC) 65–66 (IEEE, 2019).

- 10. Choi, Y. J. et al. Remote gating of schottky barrier for transistors and their vertical integration. ACS Nano 13, 7877–7885 (2019).

- Goldberger, J., Hochbaum, A. I., Fan, R. & Yang, P. Silicon vertically integrated nanowire field effect transistors. *Nano Lett.* 6, 973–977 (2006).

- 12. Xiao, Z. et al. High-density vertical transistors with pitch size down to 20 nm. *Adv. Sci.* **10**, 2302760 (2023).

- 13. Liu, L. T., Liu, Y. & Duan, X. F. Graphene-based vertical thin film transistors. *Sci. China Inf. Sci.* **63**, 201401 (2020).

- 14. Wu, F. et al. Vertical  $MoS_2$  transistors with sub-1-nm gate lengths. Nature **603**, 259–264 (2022).

- Jiang, J. et al. Ultrashort vertical-channel van der Waals semiconductor transistors. Adv. Sci. 7, 1902964 (2020).

- Schulz, T., Rosner, W., Risch, L., Korbel, A. & Langmann, U. Shortchannel vertical sidewall MOSFETs. *IEEE Trans. Electron Devices* 48, 1783–1788 (2001).

- O'Brien, K. P. et al. Process integration and future outlook of 2D transistors. Nat. Commun. 14, 6400 (2023).

- 18. Lu, D. et al. Monolithic three-dimensional tier-by-tier integration via van der Waals lamination. *Nature* **630**, 340–345 (2024).

- Tao, Q. et al. Reconfigurable electronics by disassembling and reassembling van der Waals heterostructures. Nat. Commun. 12, 1825 (2021)

- Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. *Nature* 557, 696–700 (2018).

- Li, Q. et al. Low voltage and robust InSe memristor using van der Waals electrodes integration. *Int. J. Extrem. Manuf.* 3, 045103 (2021).

- Seidel, H., Csepregi, L., Heuberger, A. & Baumgärtel, H. Anisotropic etching of crystalline silicon in alkaline solutions: I. Orientation dependence and behavior of passivation layers. *J. Electrochem.* Soc. 137, 3612–3626 (1990).

- Seidel, H., Csepregi, L., Heuberger, A. & Baumgärtel, H. Anisotropic etching of crystalline silicon in alkaline solutions: II. Influence of dopants. J. Electrochem. Soc. 137, 3626–3632 (1990).

- Hubner, U. et al. Downwards to metrology in nanoscale: determination of the AFM tip shape with well-known sharp-edged calibration structures. *Appl. Phys. A* 76, 913–917 (2003).

- 25. Li, H. et al. Optoelectronic crystal of artificial atoms in straintextured molybdenum disulphide. *Nat. Commun.* **6**, 7381 (2015).

- Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS<sub>2</sub> transistors. Nat. Nanotechnol. 6, 147–150 (2011).

- Kim, C. et al. Fermi level pinning at electrical metal contacts of monolayer molybdenum dichalcogenides. ACS Nano 11, 1588–1596 (2017).

- 28. Choi, M. S. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. *Nat. Commun.* **4**, 1624 (2013).

- 29. Radisavljevic, B. & Kis, A. Mobility engineering and a metal-insulator transition in monolayer MoS<sub>2</sub>. *Nat. Mater.* **12**, 815–820 (2013).

# **Acknowledgements**

Y.L. acknowledges the financial support from the National Key R&D Program of China (Grant No. 2021YFA1200503) and from the National Natural Science Foundation of China (Grant Nos. 51991340, 51991341, 61874041). Q.T. acknowledges the financial support from the China Postdoctoral Science Foundation (Grant No. 2023M741115). The authors acknowledge the Analytical Instrumentation Center of Hunan University for device characterization.

# **Author contributions**

Y.L. conceived the research. Y.L. Q.T. and R.W. designed the experiments. Q.T. led the device fabrication and electrical characterization. R.W., Wei L., and X.D. contributed to the CVD grown of MoS<sub>2</sub>, SEM, and STEM characterizations. X.Z., Y.C., Wanying L., Z.L., L.M., X.Y., and Lei L. assisted in the device fabrication and electrical measurement. L.K., D.L., W.S., Liting L., S.D., and X.L. contributed to discussions and data analysis. Y.L. and Q.T. co-wrote the paper. All authors discussed the results and commented on the manuscript.

# **Competing interests**

The authors declare no competing interests.

# **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-024-50185-4.

**Correspondence** and requests for materials should be addressed to Xuming Zou, Lei Liao or Yuan Liu.

**Peer review information** *Nature Communications* thanks Dinh Loc Duong, Min-Kyu Joo, and Tom Schram for their contribution to the peer review of this work. A peer review file is available.

**Reprints and permissions information** is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit <a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2024