Abstract

Impact ionization effect has been demonstrated in transistors to enable sub-60 mV dec−1 subthreshold swing. However, traditionally, impact ionization in silicon devices requires a high operation voltage due to limited electrical field near the device drain, contradicting the low energy operation purpose. Here, we report a vertical subthreshold swing device composed of a graphene/silicon heterojunction drain and a silicon channel. This structure creates a low voltage avalanche impact ionization phenomenon and leads to steep switching of the silicon-based device. Experimental measurements reveal a small average subthreshold swing of 16 µV dec−1 over 6 decades of drain current and nearly hysteresis-free, and the operating voltage at which a vertical subthreshold swing occurs can be as low as 0.4 V at room temperature. Furthermore, a complementary silicon-based logic inverter is experimentally demonstrated to reach a voltage gain of 311 at a supply voltage of 2 V.

Similar content being viewed by others

Introduction

To avoid the impact of noises and variations in the real world, an electronic device is typically required to have at least ~4 orders of magnitude on/off ratio to be used as a reliable switch in the modern electronic chips for the Boolean logic computation. This essentially mandates the threshold voltage (VTH) of the field-effect transistors (FETs) device to be at least four times of its subthreshold swing (SS). At the same time, the power consumption of the chip is proportional to the power supply voltage (VDD), a quantity that has to be larger than VTH. Therefore, the ever-increasing demand of the chips’ performance improvement and power reduction co-optimization ultimately demands the reduction of VTH at even lower off-state current (Ioff), i.e., it desires an ideal switch with minimum value of SS. Unfortunately, Boltzmann distribution of carriers in conventional metal-oxide-semiconductor FETs (MOSFETs) sets a thermionic limit of SS to be 60 mV dec−1 at room temperature1, and breaking this limit becomes inevitable for future chip technology development.

Numerous transistor architectures have been proposed at this front. For example, tunneling FETs (T-FETs)2,3,4 relying on the quantum tunneling effect instead of thermal emission of carrier is a promising choice. However, the on-state current (Ion) of such a device is low due to its band-to-band tunneling mechanism. Negative capacitance FETs (NC-FETs)5,6,7 use the dipole effect in ferroelectric material as the gate oxide layer to effectively reduce the gate voltage. However, the ferroelectric material is prone to polarization in the electric field, which restricts the low SS operation only in low-speed applications and not suitable for the gigahertz switching in most of today’s computation task. Recently, Dirac-source FETs (DS-FETs)8,9 have been proposed to achieve both low SS and high Ion by source engineering. However, it is noted that all the experimental verifications of this proposal have been conducted using low dimensional materials so far, and a demonstration of this technology in the silicon platform is still desired. Silicon-based impact ionization (II) transistors (I-MOS)10,11,12 employ the II effect of the drain/channel junction to generate feedback or floating body mechanisms in a silicon channel, and further drastically reduce the SS. However, a large drain voltage is typically required for a high electric field induced II to occur in the traditional silicon-based p-i-n I-MOS13. This contradicts the power reduction needs in the first place, and it also damages the gate dielectric and channel materials, which renders it very difficult for practical usage.

Recently, the introduction of heterojunction devices composed of two-dimensional (2D) materials has been shown to resolve some of the aforementioned issues2,3,4,5,8,9,14. For example, Miao et al. reported a gate-tunable heterojunction tunnel triode based on heterostructures composed of InSe and silicon, which offers an average SS of 34 mV dec−1 over four decades of drain current3. Gao et al. reported a ballistic I-MOS fabricated by an InSe/BP heterojunction, which has a steep SS ( < 0.25 mV dec−1) at low temperatures (T = 80 K)14. This is mainly attributed to the tunable energy band structure of 2D materials with atomically thin body, and clean vertical van der Waals heterojunctions formed by crystalline surfaces15. Since the mainstream chip process technology is still based on silicon platform, this motivates us to explore a silicon-based device architecture with a 2D material/silicon heterostructure drain, to take advantage of both the main complementary metal oxide semiconductor (CMOS) process technology as well as the properties of thin materials.

In this article, we report a vertical subthreshold swing (VS) field-effect transistor (FET) based on silicon MOSFET with graphene/silicon heterojunction (Gr-Si heterojunction) drain, i.e., the device differs from traditional silicon MOSFET only in the drain end, where graphene instead of highly doped silicon is employed to generate a superior potential drop. Gate voltage alters the graphene Fermi level to widen the depletion layer and further strengthen the electric field at this Gr-Si heterojunction. Taking these structural and electrical advantages, the device is demonstrated to achieve an average SS of 16 µV dec−1 over 6 orders of current swing and is nearly hysteresis-free at room temperature. The operating voltage at which a VS occurs can be as low as 0.4 V. Additionally, we construct a complementary logic inverter by connecting a steep n-type VSFET in series with a p-type MOSFET, achieving a voltage gain as high as 311 at a supply voltage of 2 V. Finally, the manufacturing process of the devices is largely compatible with the standard silicon process. This work opens up future opportunities for the application of silicon-based heterojunction devices in the field of energy-efficient electronics.

Results and discussion

Device structure and working mechanism

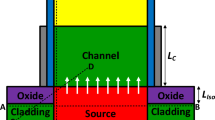

Figure 1a shows a schematic illustration of a n-type VSFET. It is composed of the top p--doped silicon in the silicon-on-insulator (SOI) as the channel and the monolayer p-type graphene (Supplementary Fig. 4) as the drain. The HfO2 is used as the gate dielectric and Ti/Au is employed for both gate electrodes and source/drain contacts. The channel width is 5 µm and the channel length is 3 µm. More details about devices fabrication flow are provided in Supplementary Note 1. The device contains a Gr-Si heterojunction drain, a silicon channel and a silicon P-N junction source. The primary mechanism for achieving a VS is believed to be the boosted II process and avalanche phenomenon taking advantage of the strong electrical field in the Gr-Si heterojunction. Schematic diagram of the energy bands of the VSFET is shown in Fig. 1 for the off (Fig. 1b) and on-state (Fig. 1c). In the off-state, the device is biased with negative top-gate voltage (VTG), and the electron injected from the source is suppressed. Graphene is a zero-gap 2D semiconductor, and its Fermi level can be tuned through electrostatic gating16,17,18. As the VTG increases, graphene transitions gradually from p-type doping to n-type doping, leading to the widening of the depletion width in the Gr-Si heterojunction. Simultaneously, the electric field at the Gr-Si heterojunction increases drastically. In addition, the energy band of the silicon channel gradually shifts downward. Electrons are more easily injected from the source into the Gr-Si heterojunction as the injection barrier in the channel decreases, as presented in Fig. 1c. As a result, carriers can obtain sufficient kinetic energy to generate electron-hole pairs within the depletion region under a strong electric field, resulting in avalanche multiplication. This is mainly because the II rate of carriers increases exponentially with the electric field19. Further, the holes created by the II accumulate in the SOI body, raising the body potential and further lowering the channel barrier height (Fig. 1c). This induces a feedback loop of more injection of electrons from source electrode and more holes generation from II at the Gr-Si heterojunction. Ultimately, this positive feedback loop helps the abrupt turn on of the device and exhibiting a near VS phenomena.

a Three-dimensional schematic of the VSFET fabricated on SOI. D, Gr, TG, S, and N + : Drain, graphene, Top-gate, Source, and N-type ion implantation area. Schematic diagram of the energy bands of the VSFET in the off-state (b) and on-state (c). EC, EV, EFS, and EFD: conduction band energy, valence band energy, source fermi level, and drain fermi level, respectively. DFT-simulated electric field contour in vertical (d) and lateral (e) direction on the VSFET. X1, X2, Z1, Z2 are line cuts in (d) and (e), respectively. f Vertical electric field of the VSFET using DFT-simulated. X1 represents the vertical electric field near the graphene-silicon heterojunction drain end, and X2 represents the vertical electric field in the silicon channel part close to the source. g Lateral electric field of the VSFET using DFT-simulated. Z1 represents the lateral electric field in the silicon region, and Z2 represents the lateral electric field in the graphene layer. h Top-view false-color SEM image of a VSFET. Scale bar, 10 µm. i Cross-sectional scanning transmission electron microscopy image of the VSFET. Corresponding EDS elemental map showing the distribution of C and Si elements. j The zoom-in image in the orange rectangle in (i). Scale bar, 2 nm. k Comparison of experimentally measured logarithmic-scale transfer characteristics of the fabricated VSFET (red curve) and MOSFET (blue curve) at VDS = 3 V.

To confirm the enhanced II located at the Gr-Si heterojunction, the electric field distribution is calculated using density functional theory (DFT)/non-equilibrium Green’s function (NEGF). The vertical and lateral electric field contours of the VSFET at a source-drain bias voltage (VDS) of 1 V are displayed in Fig. 1d, e, respectively. Both vertical electric field and lateral electric field are peaked around the graphene and silicon heterojunction drain end. The magnitude of the vertical electric field at the Gr-Si heterojunction reaches 17.6 MV cm−1, more than 4.3 times higher than that close to the source side where no heterojunction exists, as illustrated in Fig. 1f. This enhancement is attributed to the high carrier concentration of graphene and recessed edge20. Moreover, the lateral electric field peak in the VSFET occurs within the silicon region of the Gr-Si heterojunction drain and reaches 12.1 MV cm−1, more than 6.5 times higher than that of the normal silicon source P-N junction, as shown in Fig. 1g. And a detailed analysis using DFT/NEGF calculations is presented in Supplementary Note 3. We also use computer-aided design (TCAD) simulations with Synopsys Sentaurus to study the device characteristics. The simulated transfer characteristic curve shows a steep switching characteristic. A detailed TCAD simulation analysis is shown in Supplementary Note 4.

The layout of the device is shown in a false-color scanning electron microscopy (SEM) image (Fig. 1h), illustrating the connection of the graphene drain to both the metal electrode and the silicon channel. A cross-sectional transmission electron microscopy (TEM) image of a typical VSFET is displayed in Fig. 1i. Additionally, a detailed elemental map obtained through energy-dispersive X-ray spectrometry (EDS) reveals a uniform carbon layer along with silicon, confirming the even distribution of graphene on the silicon surface. Cross-sectional TEM images of the magnified dotted rectangle region are presented in Fig. 1j. The interface between graphene and silicon exhibits atomically smooth characteristics, free from impurities and minimizing defects, indicating a high-quality Gr/Si interface with negligible impurities and atomic defects. The VSFET has a steep SS as opposed to Si MOSFET (Fig. 1k) fabricated in similar process conditions, and the Ion of both devices reach at the same level at 0.75 V gate bias. The VSFET also exhibits significantly reduced ambipolar characteristics, with a high current on/off ratio of > 106 at VDS = 3 V.

Electrical characterization of VSFET

The electrical characteristics of the device are presented in Fig. 2a–d. Figure 2a shows the transfer characteristic of a n-type VSFET at various back-gate voltages (VBG). The VTG controllability of the device current is improved by increasing the VBG in the negative direction. Additionally, the device electrical characteristics exhibits VS behavior when the VBG is –10 V. These phenomena are mostly attributed to the following mechanism. On the one hand, the increase of VBG in the negative direction raises the barrier height of the bottom silicon channel, making it difficult for the electrons to move across and reach the Gr-Si heterojunction, which reduces the Ioff of the device. On the other hand, it strengthens the electric field at the Gr-Si heterojunction, which activates the avalanche multiplication of carriers in the device when the VBG reaches a particular threshold, causing the device to abruptly switch from the off-state to the on-state. It is noted in principle that the device should still be able to produce the VS phenomena by controlling the doping concentration in the silicon channel without applying a VBG (Supplementary Fig. 7). In addition, as the VBG further increases, the Ioff of the device also rises. This increase can be attributed to the decrease in the depletion width at the Gr-Si heterojunction, which in turn facilitates the diffusion current to easily pass through the heterojunction. When the VBG is fixed at -15 V, sub-60mV dec-1 steep slope of SS is consistently observed at various VDS. As VDS increases, the Ion gradually increases (Fig. 2b). This superior electric field at the Gr/Si heterojunction enables steep SS even at a low VDS as low as 0.4 V (Fig. 2b inset). And similar results are repeated in multiple devices as shown in Supplementary Fig. 8. Additionally, the gate-leakage current is negligible compared to the drain current (Supplementary Fig. 9). Figure 2c shows the statistical distribution of SS for 30 n-type VSFETs. Note that all devices show SS below 10 mV dec–1, indicating the reproducibility of the fabricated devices. The smallest average SS of our device approaches 16 µV dec-1 over 6 orders of magnitude (Fig. 2d), the lowest value among all existing silicon-based FETs. We also study the impact of the scan step size of the top gate voltage on the SS of the device (Supplementary Fig. 10), and it is discovered that the measured SS is still likely to limited by the instrument resolution, i.e., the real SS can be even steeper with a smaller measurement step size. Moreover, multiple devices have also tested similar SS values (Supplementary Fig. 10c). The VSFET clearly exhibits well-behaved rectifying output characteristics, featuring a rectification ratio of approximately 1 × 106 (Supplementary Fig. 11b). A p-type VSFET can be realized by replacing the n-type doping at the ion implantation with p-type doping. The transfer characteristics of the device are presented in Fig. 2e, f. Compared with the n-type VSFET, the p-type VSFET shows similar electrical characteristics except the Ion is relatively weaker, which could possibly be attributed to the lower carrier mobility of holes and/or the unoptimized fabrication process for p-type device.

a Transfer characteristics of the n-type VSFET with back-gate voltages from 0 V to -20 V with a step of –5 V. b Transfer characteristics of the n-type VSFET with bias voltages from 1.5 V to 3 V. The inset is the transfer characteristic curves at VDS = 0.4 V. c SS versus output current IDS of 30 representative n-type VSFETs showing reproducibility of the effect at VDS = 3 V. The inset is the statistical distribution of SS for these n-type VSFETs (the voltage scanning step is 50 mV). d Transfer characteristics of the n-type VSFET measured with voltage scanning step of 0.1 mV. The bias voltage of VDS is 3 V and the temperature is 300 K. e Transfer characteristics of the p-type VSFET with back-gate voltages from 0 V to 20 V. f Transfer characteristics of the p-type VSFET with drain bias voltages from –2 V to −3 V.

To further verify the transport mechanism of the VSFET, we conduct temperature-varying tests on the steep transfer characteristics (Supplementary Fig. 12), and the extracted SS is shown in Fig. 3a. In contrast to typical MOSFET, which exhibits a linear temperature relationship due to the Boltzmann distribution (2.3 kT q–1, blue line), the SS of the VSFET is rather insensitive to temperature variations (red line), confirming the subthreshold transport is not from thermionic emission. In addition, the current noise density spectra are measured under various VTG from –3 V to 3 V, and the normalized noise power spectral density, S(f)/I2 is shown in Fig. 3b. All the spectral density exhibits typical 1/f behavior. It is also discovered that the normalized noise power density in the on-state is lower than that in the off-state. The device rapidly turns on as an avalanche of carriers is activated, creating a significant amount of current. After the device is turned on, its normalized noise power density tends to saturate and remains constant regardless of the change in the VTG. This indicates that the carriers inside the device have stabilized and are no longer impacted by the carrier multiplication, which is advantageous for the reliability of the device. This is further demonstrated by the detailed repeatability tests exhibited in Supplementary Fig. 13. Figure 3c displays the forward and reverse transfer characteristic curves of one device and it shows a very small hysteresis window (approximately 50 µV), benefiting from the high-quality interface between the graphene and silicon. The fact that our device exhibits a hysteresis-free window suggests that its working principle goes beyond a pure feedback device mechanism21, and this makes VSFET more feasible for low-power logic systems. Figure 3d benchmarks the SS as a function of normalized drain current for a VSFET and various types of existing sub-thermionic FETs, including T-FETs3,22,23, NC-FETs24,25 and DS-FETs8,9 at room temperature. Where the SS versus IDS for the VSFET is extracted from the transfer curves (Supplementary Fig. 10b). The average SS of VSFET remains significantly low (« 1 mV dec–1) over 6 orders of magnitude, and the steepest range exists in the entire subthreshold region, exhibiting an ideal current switching behavior. Furthermore, the VSFET shows a superior I60 current (the current when the subthreshold SS is equal to 60 mV dec–1) density (∼26 μA μm–1), higher than any TFET technologies reported.

a The SS as the function of temperature. Blue curve is theoretical value which follows the Boltzmann limitation (2.3 kT q–1), and the red curve is the experimentally measured results of the n-type VSFET. b Normal noise power spectral density versus frequency for different top gate voltages at room temperature. The tilted black dashed line is the standard 1/f noise guideline. c Forward and reverse transfer characteristic curves of VSFETs. The inset-left is the corresponding transfer characteristic curves of p-type VSFET. The inset-right is the transfer characteristic curves of IDS from 10−10 to 10-9 A, showing that the device exhibits a nearly free hysteresis of 50 µV. d Benchmarking of the n-type VSFET with other state-of-the-art steep-slope transistor technologies3,8,9,22,23,24,25. Subthreshold swing as a function of drain current for various types of sub-thermionic FET. The gray dashed line represents the SS = 60 mV dec−1 limit.

Complementary inverter composed of the VSFET

The characterization of a complementary inverter utilizing a combination of p-type MOSFET and n-type VSFET are accomplished. The corresponding circuit diagram is depicted in Fig. 4a. Transfer characteristics of the p-type MOSFET and n-type VSFET are illustrated in Fig. 4b. Additionally, Fig. 4c represents the voltage transfer characteristics of the inverter, along with the voltage gain (Vgain) exhibiting the input voltage (VIN) under supply voltages (VDD) of 1.5 V and 2 V, respectively. The output voltage (VOUT) is high (logic “1”) when the input voltage (VIN) is low (logic “0”). As VIN increases (logic “1”), VOUT is pulled down to a low level (logic “0”). This illustrates the logic operation of this inverter. High VOUT values are close to VDD and low VOUT values are close to 0.1 V, indicating a good VTH match between these two devices. The Vgain increases as VDD increases, reaching a peak value of 311 when VDD is 2 V, and this is considerably higher in comparison with any existing silicon-based MOSFET inverters. In addition, with the increase of the VDD, the transition voltage (VM) exhibits a right-shifting tendency toward positive VIN. We also analyze the effect of the SS of the steeper device on the Vgain of the complementary inverter. The calculation results show that the inverter’s Vgain increases with decreasing SS (Supplementary Note 11). Figure 4d is the benchmark of the Vgain as a function of VDD, it is not only higher than another steep switching devices26,27,28,29,30, but also advantageous compared to reported 2D semiconductor-based CFETs31,32,33,34,35, and silicon-based CFETs36,37,38.

a Three-dimensional schematic, and circuit configuration of the inverter. b Transfer characteristics of n-type VSFET and p-type MOSFET (blue and pink curves, respectively). c The voltage transfer characteristics and gains of the inverter under VDD = 1.5 and 2.0 V. d Benchmark of inverter gain as a function of VDD for inverters based on steep switching devices26,27,28,29,30, 2D semiconductor-based CFETs31,32,33,34,35, silicon-based CFETs36,37,38 and VSFET in this work.

In summary, we have successfully demonstrated a silicon-based VSFET with nearly vertical subthreshold swing. Thanks to the Gr-Si heterojunction drain, the electric field in the silicon close to the drain end is significantly enhanced and this drastically boosts the II rate. Taking this major advantage, sharp switching behavior can be observed under supply voltage as low as 0.4 V, and the device exhibits an average SS of 16 µV dec-1 over 6 decades of drain current and nearly hysteresis-free (<50 µV) at room temperature. Furthermore, we experimentally demonstrate a high-performance complementary FET inverter composed of traditional MOSFET and VSFET. This inverter exhibits a voltage gain as high as 311 at a supply voltage of 2 V. This research paves the way for developing silicon-based devices in energy-efficient electronics.

Methods

Device fabrication

The VSFET was formed by transferring chemical vapor deposition (CVD) grown graphene onto pre-patterned SOI substrates. The pre-patterned was carried out on an SOI substrate. The mesa isolation was formed by photolithography followed by wet etching. Photolithography was then used to define the silicon channel and ion implantation regions. Then, ion implantation of Arsenic ions was used to form n+ doping for the ion implantation regions. Multiple Ti/Au electrodes were patterned and deposited using photolithography and electronic beam evaporation, acting as the source and drain. The CVD grown graphene purchased from ACS Material, LLC. was transferred from a copper substrate to a pre-patterned SOI substrate and then patterned as drains of the device by photolithography and O2 reactive ion etching (RIE). Since there are no dangling bonds on the surface of the graphene, it is difficult to grow HfO2 directly through atomic-layer deposition (ALD) technology, so ~2 nm SiO2 was deposited as a seed layer before growing HfO2. The HfO2 layer was grown by ALD technology as a high-k dielectric layer. The top gate was patterned and deposited using photolithography and E-beam evaporation of Ti/Au films.

Material characterization and electrical measurement

The structure of the device was confirmed through cross-sectional high-resolution transmission electron microscopy using an FEI Titan3 G2 60-300, coupled with energy dispersive X-ray spectroscopy. The scanning electron microscopy image was obtained using a Zeiss Sigma 300. Electrical measurements were conducted using Keithley 2636B and 2612B source/meters. All electrical measurements were carried out in a vacuum probe station under dark conditions at room temperature, except for specific variable temperature tests. The noise was assessed using a noise measurement system (PDA NC300L).

Data availability

The data that supports the findings of this study are available at https://zenodo.org/records/13756121. All other data are available from the corresponding authors upon request.

Code availability

The codes used for simulation and data plotting are available from the corresponding authors upon request.

References

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Kim, S. et al. Thickness-controlled black phosphorus tunnel field-effect transistor for low-power switches. Nat. Nanotechnol. 15, 203–206 (2020).

Miao, J. et al. Heterojunction tunnel triodes based on two-dimensional metal selenide and three-dimensional silicon. Nat. Electron. 5, 744–751 (2022).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

McGuire, F. A. et al. Sustained sub-60 mV/decade switching via the negative capacitance effect in MoS2 transistors. Nano Lett. 17, 4801–4806 (2017).

Rusu, A., Salvatore, G. A., Jimenez, D. & Ionescu, A. M. Metal-ferroelectric-meta-oxide semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification. In IEEE International Electron Devices Meeting. 16.13.11-16.13.14 (IEEE, 2010).

Khan, A. I., Yeung, C. W., Hu, C. & Salahuddin, S. Ferroelectric negative capacitance MOSFET: Capacitance tuning & antiferroelectric operation. In IEEE International Electron Devices Meeting. 11.13.11-11.13.14 (IEEE, 2011).

Liu, M. et al. Monolayer MoS2 steep-slope transistors with record-high sub-60-mV/decade current density using Dirac-source electron injection. In IEEE International Electron Devices Meeting. 12.15.11-12.15.14 (IEEE, 2020).

Qiu, C. et al. Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches. Science 361, 387–392 (2018).

Onal, C. et al. A novel depletion-IMOS (DIMOS) device with improved reliability and reduced operating voltage. IEEE Electron Device Lett. 30, 64–67 (2008).

Gopalakrishnan, K., Griffin, P. B. & Plummer, J. D. I-MOS: a novel semiconductor device with a subthreshold slope lower than kT/q. In Digest. International Electron Devices Meeting. 289-292 (IEEE, 2002).

Gopalakrishnan, K. et al. Impact ionization MOS (I-MOS)-part II: experimental results. IEEE Trans. Electron Devices 52, 77–84 (2004).

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Gao, A. et al. Observation of ballistic avalanche phenomena in nanoscale vertical InSe/BP heterostructures. Nat. Nanotechnol. 14, 217–222 (2019).

Geim, A. K. & Grigorieva, I. V. Van der Waals heterostructures. Nature 499, 419–425 (2013).

Yang, H. et al. Graphene barristor, a triode device with a gate-controlled Schottky barrier. Science 336, 1140–1143 (2012).

Novoselov, K. S. et al. Two-dimensional gas of massless Dirac fermions in graphene. Nature 438, 197–200 (2005).

Xia, F. et al. The origins and limits of metal-graphene junction resistance. Nat. Nanotechnol. 6, 179–184 (2011).

Chynoweth, A. Ionization rates for electrons and holes in silicon. Phys. Rev. 109, 1537 (1958).

Zhang, D. et al. 0.5T0.5R-An ultracompact RRAM cell uniquely enabled by van der Waals heterostructures. IEEE Trans. Electron Devices 68, 2033–2040 (2021).

Padilla, A. et al. Feedback FET: A novel transistor exhibiting steep switching behavior at low bias voltages. In IEEE International Electron Devices Meeting. 1-4 (IEEE, 2008).

Convertino, C. et al. A hybrid III-V tunnel FET and MOSFET technology platform integrated on silicon. Nat. Electron. 4, 162–170 (2021).

Huang, Q. et al. A novel Si tunnel FET with 36 mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration. In IEEE International Electron Devices Meeting. 8.5.1-8.5.4 (IEEE, 2012).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Zhou, J. et al. Ferroelectric HfZrOxGe and GeSn PMOSFETs with Sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved IDS. In IEEE International Electron Devices Meeting. 12.12.11-12.12.14 (IEEE, 2016).

Wang, X. et al. Van der Waals negative capacitance transistors. Nat. Commun. 10, 3037 (2019).

Wang, J. et al. Low‐power complementary inverter with negative capacitance 2D semiconductor transistors. Adv. Funct. Mater. 30, 2003859 (2020).

Choi, W. Y. et al. 70-nm impact-ionization metal-oxide-semiconductor (I-MOS) devices integrated with tunneling field-effect transistors (TFETs). In IEEE International Electron Devices Meeting. 955-958 (IEEE, 2005).

Choi, H. et al. A steep switching WSe2 impact ionization field-effect transistor. Nat. Commun. 13, 6076 (2022).

Knoll, L. et al. Inverters with strained Si nanowire complementary tunnel field-effect transistors. IEEE Electron Device Lett. 34, 813–815 (2013).

Tosun, M. et al. High-gain inverters based on WSe2 complementary field-effect transistors. ACS Nano 8, 4948–4953 (2014).

Koenig, S. P. et al. Electron doping of ultrathin black phosphorus with Cu adatoms. Nano Lett. 16, 2145–2151 (2016).

Liu, T. et al. Nonvolatile and programmable photodoping in MoTe2 for photoresist‐free complementary electronic devices. Adv. Mater. 30, 1804470 (2018).

Huang, M. et al. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Pu, J. et al. Highly flexible and high‐performance complementary inverters of large‐area transition metal dichalcogenide monolayers. Adv. Mater. 28, 4111–4119 (2016).

Chang, S.-W. et al. First demonstration of CMOS inverter and 6T-SRAM based on GAA CFETs structure for 3D-IC applications. In IEEE International Electron Devices Meeting. 11.17.11-11.17.14 (IEEE, 2019).

Chang, S.-W. et al. First demonstration of heterogeneous IGZO/Si CFET monolithic 3-D integration with dual work function gate for ultralow-power SRAM and RF applications. IEEE Trans. Electron Devices 69, 2101–2107 (2022).

Tong, L. et al. Heterogeneous complementary field-effect transistors based on silicon and molybdenum disulfide. Nat. Electron. 6, 37–44 (2023).

Acknowledgements

This work was supported in part by National Key Research and Development Program (Grant No. 2021YFA-1200500). Natural Science Foundation of China (Grant No. 62374034, 62350610270). Innovation Program of Shanghai Municipal Education Commission (Grant No. 2021-01-07-00-07-E00077) and Natural Science Foundation of Shanghai (Grant No. 22ZR1403500). The support from Young Scientist Project of MOE Innovation Platform is also appreciated. Y.Z. acknowledges support from the New Cornerstone Science Foundation.

Author information

Authors and Affiliations

Contributions

Y.L., J.Wan, and J.X. conceived and supervised the project. B.Y. wrote the manuscript, and Y.L., J.Wan, and P.Z. revised the manuscript. B.Y., Z.C., and Y.C. fabricated the devices. B.Y. performed the electrical measurements and data processing with assistance from C.T. and W.C. C.Z., Z.H., Q.Z., and J.Wang contributed to the working mechanism analysis. Z.H. and W.G. contributed to the TCAD simulation analysis. Q.Z. and J.G. contributed to the DFE/NEGF simulation analysis. M.L. and Y.Z. contributed to the temperature-varying tests. Y.L., Z.C., G.H., Z.W., K.L., Z.Z., S.X., C.C., W.B., and S.M discussed the results. All authors commented on the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks He Tian and the other anonymous reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Yuan, B., Chen, Z., Chen, Y. et al. High drain field impact ionization transistors as ideal switches. Nat Commun 15, 9038 (2024). https://doi.org/10.1038/s41467-024-53337-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-024-53337-8