Abstract

The comprehension of the governing mechanism which affects device instability is one of the most important requirements for the formation of reliable oxide-thin film transistors (TFTs). However, a quantitative analysis of the dominant mechanism of device instability, which stems from charge trapping induced by defects at the oxide semiconductor interface as well as in its bulk, has not yet been systematically performed. In this study, we examined subgap states, charge-transport dynamics, and various trap characteristics of oxide TFTs by multi-frequency C–V, pulse I–V, and transient current methods to achieve a comprehensive understanding of carrier transport and charge trapping mechanisms. We found that the charge trapping behavior of the tested amorphous InHfZnO (a-IHZO) TFT follows a multi-trapping mechanism, such as temperature-independent fast transient charge trapping by resonant drift of the injected electron and temperature-dependent slow transient charge trapping by charge transport from occupied to unoccupied traps. Understanding fast charging and slow charging described in this study can help to understand the root cause of device instability of oxide TFTs and ultimately improve stability and reliability characteristics.

Similar content being viewed by others

Introduction

In recent times, amorphous oxide semiconductor-based TFTs have been attracting enormous attention for display applications1,2,3,4,5, owing to their steep subthreshold slope (~0.2 V/decade), high field-effect mobility (5–100 cm2/eV·s), and low-temperature fabrication process6,7,8. High field-effect mobility enables fast switching, which is especially important for display technology9,10. In this research area, various amorphous-oxide semiconductor materials, such as InGaZnO, InHfZnO and InSnZnO have been studied to secure high stability and high reliability while maintaining high mobility11,12,13,14,15,16,17. However, the device instability and reliability issues of amorphous oxide semiconductor-based TFTs remain as potential issues faced by their production18,19,20,21,22,23. Interfacial and bulk defects in amorphous-oxide semiconductors result in significant charge trapping effects, leading to device instability and reliability issues. Therefore, an accurate understanding and precise management of defects in oxide semiconductors are required for the success of oxide TFTs24,25,26,27,28,29. The study of the fast and slow charge trapping were reported by many groups with various methods. Ramon et al., reported that the fast and slow charge trapping were investigated using the charge pumping technique30. U. Jung et al., suggested that the quantitative estimation of defects contributing to charge trapping using the discharge current analysis method31. These previous studies suggested that charge trapping is affected by both shallow (interface) and deep state (bulk) defects. Despite these studies, however, possible origins and information about locations of charge trapping remains unclear.

In our work, we investigated fast and slow transient charging behaviors in oxide TFTs and their effects on electrical characteristics. To this end, we employed a multi-frequency measurement (MFM) technique to evaluate the subgap density of states (DOS)32 as well as pulse I–V (PIV) and transient current methods to study time-dependent charge trapping phenomena33,34,35,36,37,38,39,40,41,42. In addition, we consider a model for electron charging behavior of oxide TFTs utilizing measurements of transient current with temperature. This shows that transient charge trapping follows two different type processes such as a fast electron charging process where electrons are injected into shallow defects (fast transient charging) and thermally activated electron migration via trap-to-trap conduction (slow transient charging). The former is responsible for mobility degradation and V TH instability, while the latter is responsible for long-time stress V TH instability. As a result of this study, it was found that DOS through MFM measurement technique was exponentially distributed in the shallow energy state region, and fast & slow charge trapping occurred relatively shallow energy in range of less than 0.4 eV below the conduction band minimum through short and long pulse measurement technique. This model enables comprehension of the dynamic charge trapping behavior of oxide TFTs43.

Results

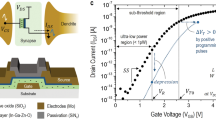

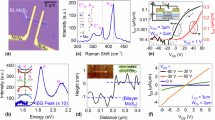

Inverse staggered TFTs with a-IHZO semiconductor and molybdenum metal electrodes were fabricated. Schematics of a fabricated oxide TFT and a high annular transmission electron microscopy image are presented in Fig. 1(a) and (b), respectively. The semiconductor material composition was verified by analyzing the energy dispersion spectrometry, shown in Fig. 1(c) and the structure was confirmed by a transmission diffraction pattern (see the inset of Fig. 1(c)). After the fabrication of the a-IHZO TFTs, in order to confirm the influence of the Hf content on the IHZO films, the transient current versus charging time curves (the charging time range is from 5 µs to 5 ms.) were measured with various Hf contents, as shown in Fig. 2(a). The charge trapping effect causes a reduction in the drain current with time. The threshold voltage shift (ΔVth) was determined from the transient current versus charging time curves by using the equation, ΔVth = ΔIDS·(VGS − Vth)/IDS. Where ΔIDS is difference of the drain current during the pulse width (charging time), IDS is the maximum value of the drain current before the pulse width, VGS is the pulse amplitude, and Vth is the threshold voltage. From this equation, distributions of ΔVth were plotted with respect to charging time, as shown in Fig. 2(b). Then, the critical charge trapping time (tc) was determined. We found that tc increased with decreasing Hf content in the a-IHZO (tc values of 4, 7, and 10 mol% Hf content in the a-IHZO TFT are 1.98 μs, 858 ns, and 509 ns, respectively). Therefore, the Hf content in a-IHZO films obviously influences charge trapping mechanism. This experimental results showed that the incorporation of high Hf content in a-IHZO semiconductor increased the defect density, resulting in device instability.

For a comparative study of the effect of defects on the charge trapping phenomena of oxide TFTs, we employed two different gate insulators, Si3N4 and SiO2, which significantly influence the interfacial and bulk quality owing to the strain effect, different atomic configuration, and hydrogen content. The left-hand graph of Fig. 3(a) shows the DC I–V and fast I-V (FIV) measurement data for the a-IHZO TFTs with Si3N4 and SiO2. The drain current levels and subthreshold slopes (S.S.fast, SiO2 of 0.12 V/dec., S.S.DC, SiO2 of 0.18 V/dec., S.S.fast, Si3N4 of 0.13 V/dec., and S.S.DC, Si3N4 of 0.20 V/dec.) were determined by transfer curve. Those measured by the FIV technique were better than those measured by the DC I-V technique. The S.S. value can be changed to the total trap density (Ntot) using the following equation (1).

Where N total is the total trap density, kT is the thermal energy, q is the elementary charge and C ox is the gate insulator capacitance. The Ntot values of IHZO with SiO2(Fast I-V), IHZO with SiO2(DC I-V), IHZO with Si3N4(Fast I-V) and IHZO with Si3N4(DC I-V) TFTs are 4.37 × 1010, 8.72 × 1010, 5.1 × 1010 and 1.02 × 1011 cm−2 ev−1, respectively. In addition, we added the values of subthreshold slope to the following sentence.

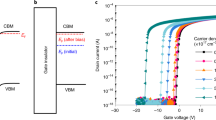

As presented in the right-hand graph of Fig. 3(a), the mobility values obtained by the FIV technique (μ fast, Si3N4 = 14.79 cm2/eV·s and μ fast, SiO2 = 12.1 cm2/eV·s) are, as expected, superior to those measured by the DC I–V technique (μ DC, Si3N4 = 11.42 cm2/eV·s and μ DC, SiO2 = 9.8 cm2/eV·s). The device in which Si3N4 is used as the gate insulating film shows higher drain current than that with SiO2 gate insulator. The use of a mixed gas of silane (SiH4) and ammonia (NH3) as a source gas during Si3N4 deposition leads to have a high concentration of hydrogen in Si3N4, acting as donor to the oxide semiconductor, shifting the threshold voltage of TFT toward negative gate bias direction due to high carrier concentration. In accordance with the percolation model, mobility increases in proportion to the carrier concentration44,45. Certainly, as shown in Fig. 3(a), Si3N4 devices exhibit high mobility. In agreement with earlier reports regarding metal oxide semiconductor field-effect transistors (MOSFETs), the DC I−V techniques used to extract various device parameters require comparatively long sweep/measurement times, such as a few seconds to tens of seconds, causing fast transient charge trapping and resulting in the underestimation of device performance33,34,35,36,37,38,39,40,41,42. Even for an a-IHZO TFT with SiO2 gate insulator, we observed significant differences in the value of drain current and mobility value measured by the DC I−V and FIV techniques. Moreover, the ratio of the mobilities, μ fast:μ DC, is higher for the a-IHZO TFT with Si3N4 gate insulator (29.5%) than for the a-IHZO TFT with SiO2 (23.5%), as presented in Fig. 3(a), indicating that the Si3N4 device is susceptible to fast charging. This was verified by the energy-dependent subgap DOS measured by MFM. The subgap DOS extraction of a-IHZO TFTs with two different gate insulators was begun by measuring the frequency-dependent capacitance−voltage (C−V) between source/drain electrodes and gate electrode, using an LCR meter32. Subsequently, we adopted the model (MFM) that was proposed by S. Lee and D. H. Kim and finally obtained a frequency-independent C−V and energy-dependent subgap DOS, as shown in Fig. 3(b) 32. The acceptor-like DOS of the a-IHZO TFT with Si3N4 gate insulator is higher than that of the a-IHZO TFT with SiO2 gate insulator. Table 1 summarizes the parameters of gate-insulator-dependent subgap DOS from the model g(E) = N TA ·exp{(E-E C )/kT TA } + N DA ·exp{(E-EC)/kT DA }, where N TA is the acceptor like tail state density, kT TA is the acceptor like tail state characteristic energy, N DA is the acceptor like deep state density, and kT DA is the acceptor like deep state characteristic energy.

To further understand the defects and transient charging mechanism, the a-IHZO TFTs were subjected to a constant bias, short pulse, and long pulse stresses under measurement temperatures ranging from 25 to 175 °C43. To observe the threshold voltage (V TH ) shift, after a constant bias stress duration, the electrical stress was stopped and the DC I-V was measured43.

Consistent with previous studies, we confirmed that under low bias stress, electron trapping shows a reversible phenomenon by applying de-trapping (opposite polarity) voltage43. As shown in Fig. 4(a), the V TH value can be returned to the value before applying the stress voltage. Also, the dependence of the V TH value under the bias stress (stress voltage of 8 V) hardly changes with each stress cycle. In addition, subthreshold slope (S.S. SiO2 of 0.18 V/dec., and S.S. Si3N4 of 0.20 V/dec.) is almost not affected by the bias stress. Thus, we believe that electron trapping takes place in pre-existing defects. Additionally, the low bias stress applied to the device does not generate a considerable number of defects. Figure 4(a) shows an initial sharp increase in V TH for the first second of constant bias stress. To examine the initial charge trapping for the different quality of major charge transport layer, front channel (the channel near to the gate insulator) with relatively shallow energy, we performed a PIV technique on the a-IHZO TFTs with two different gate insulator materials such as Si3N4 and SiO2 33,34,35,36,37,38,39,40,41,42. The PIV measurement schematics is presented in Fig. 4(b). A square wave pulse was applied to the gate electrode. The rise and fall times were both 10 µs and pulse width time was 2 ms. The gate voltage pulse was 8 V (Fig. 4(c)).

(a) Threshold voltage shift in a-IHZO TFTs during stress cycles, which include 1000 s at V GS = 8 V followed by 0.1 s stress at the opposite bias of -1 V. (b) Schematic of pulse I-V measurement system (c) Pulse I-V characteristics (left) and corresponding transient current versus time characteristics (right) of a-IHZO TFTs with SiO2 and Si3N4 gate insulators.

Figure 4(c) displays the PIV (left-hand graph) as well as transient current (right-hand graph) data. During the positive-bias pulse width, the degradation of the source to drain current (ΔI DS ) results from the variation of threshold voltage (ΔV TH ) owing to the trapped charge in the front channel ΔI DS = (W/L)·C ox ·μ·ΔV T , where W and L are the TFT channel width and length, respectively, C ox is the gate oxide capacitance, and μ is the carrier mobility. According to the equation above, ΔV TH can be calculated from ΔI DS :

where ΔI DS is the difference in the source to drain current between the end and start of the gate bias pulse, I DS is the maximum source to drain current prior to charge trapping, V GS is the gate voltage pulse amplitude, and V TH is the threshold voltage.

The charge trapping in the pre-existing defects through several processes is described in Fig. 5. Electrons drift to the front channel and are charged in acceptor like defects [process P C in Fig. 5]. Then, it follows temperature-dependent electron transfer between the defects (process P T ). In oxide semiconductor channel, when acceptor-like defects are filled with electrons, they became electrically negative, which contributes to ΔV TH and ΔI DS . As will be discussed below, a noticeable feature of acceptor-like defects in the front channel that contribute to fast and slow transient charging is that their energy states are located in a relatively shallow energy range of <0.4 eV below the conduction band minimum. The charging process P C is expected to have a short charging characteristic time because of the very low trap energy and high DOS in the a-IHZO conduction band. Thus, the charging process P C is the major constituent of fast transient charging. Here, we concentrate on fast transient charge trapping induced by P C (fast component) and slow transient charge trapping caused by temperature-activated electron transport, P T (slow component). At the beginning of the constant bias stress, the initial (~100 μs) increase in ΔV TH (see, for example, Fig. 4(a)) is comparable to the ΔV TH obtained by the PIV measurement method in the μs range, while during the subsequent bias stress of several seconds, ΔV TH gradually increases with stress time, contributing to the observed stress-time-dependent ΔV TH . This indicates that there are two charging processes with different charging characteristic time. We found that fast transient charging (P C ) occurs in the μs range and slow transient charging (temperature-dependent charging, P T ) starts to take place after a few seconds. Thus, fast transient charging (P C ) is significantly responsible for the initial ΔV TH (Fig. 4(a)). Different time scales, such as 10−6–10−4 s (fast component) and 10–103 s (slow component), allow the categorization of fast and slow processes, as described in the model.

Fast transient charging

To investigate fast and slow charging, we applied a simplified model proposed by G. Bersuker43. In this model, we assume that channel electrons drift to the defects and can be negatively charged when they occupy defects whose energies are in quasi-resonance. Following the assumption above, equation (3) shows the kinetics of fast charging. And the solution of this equation can be represented by Eq. (4):

Where, n is the density of the occupied traps, t is the time, p is the probability of a electron-trapping event, N 0 is the total density of available traps.

To evaluate the influence of temperature on fast transient charging, the transient current versus time characteristics of the a-IHZO TFTs with SiO2 and Si3N4 gate insulators were measured by applying a short pulse (100 µs) at 25 to 125 °C (Fig. 6(a) and (b)). As such in previous study46, as seen in Figs 6(a) and 5(b), the source to drain current tends to increase with increasing measurement temperature. According to the model, more electrons escape from the localized state at relatively high measurement temperature46. On the other hand, ΔI DS for the initial 20 μs of the pulse width is almost the same regardless of measurement temperature, as seen in Fig. 6(c). A representative example of fitting Equation (4) to the measured source to drain current with time for Si3N4 and SiO2 gate-insulator-stacked a-IHZO devices is presented in Fig. 6(c), where the fitting was performed to ΔI DS for the initial 20 μs of the pulse width in Fig. 6(a) and (b), which is much shorter than the time it takes for the ΔI DS to saturate. We should notice that time dependence of the drain current does not depend on temperature, representing that fast charging is not a temperature-activated process. The obtained N 0 is of the order of 1013 cm−2 (Si3N4 gate insulator) and 1012 cm−2 (SiO2 gate insulator). Coulomb repulsion, which prevents charge trapping at most available defect sites, acts between trapped charges, the final density seems to be low.

Source to drain current of the a-IHZO TFTs with (a) SiO2 and (b) Si3N4 gate insulators during the pulse width (100 µs) at the gate pulse V GS of 8 V measured at various temperatures. (c) Source to drain current shift during the initial 20 µs of the pulse in Fig. 5(a) and (b).

Slow transient charging

It has been demonstrated in previous studies that slow transient charging is as effectively de-trapped as fast transient charging, under the same detrapping voltage47,48. This shows that traps with fast and slow transient charging have similar detrapping kinetics, suggesting that the traps of the two types of charging have similar physical characteristics. The model we apply and study begins with the assumption that the fast and slow transient charging occur in the same traps43.

In accordance with the slow transient charging model, slow transient charging might be attributed to the capture of secondary electrons, which stem from the traps, charged by the fast drift process (P C ) (Fig. 5)43. Thus, when some trapped electrons are activated from the traps by thermal energy and are hopping over the conduction band minima, they can be re-trapped in the surrounding empty traps before these electrons gain sufficient kinetic energy. This is the trap-conduction band-trap process (P T ) (Fig. 5).

The fast (microsecond scale) and slow (second scale) transient charging have a very large difference in charging characteristic time scale, so a fast drift charging process occurs immediately in the traps where thermally activated detrapping occurs and this continuously provides activated electrons to continue the slow transient charging.

The slow transient charging process can be expressed in the form Eq. (5)

where N is the trap density, N S is the density of the secondary traps positioned close the filled traps, and p s (i) = σ s J s (i), where σ s is the capture cross-section for the electrons, and J s expressed in Eq. (6) is defined by electrons that are thermally activated and emitted from the traps (Fig. 5).

where J is the current density, n is the density of the occupied fast traps, τ is the de-trapping time constant, E i is the trap energy, k is the Boltzmann constant, and T is the temperature.

The transient current was measured by applying a long pulse stress (pulse width: 1000 sec.) to the a-IHZO TFTs with SiO2 and Si3N4 gate insulators at a temperature from 25 to 125 °C to verify the temperature dependent slow transient charging model described above. Representatively, the measured data for the a-IHZO TFT with SiO2 device is shown in Fig. 7(a). The results of fitting the ΔV TH values for the whole temperature range using Eq. (5) are shown in Fig. 7(b). The fitting was repeatedly carried out by increasing the terms one by one, starting with a single term in the sum of Eq. (5). Fitting the Eq. (5) in Fig. 7(b) requires two terms, which implies that slow charging occurs in more than one type of defects. The fitting of equation (6) for all temperature data requires two terms, i = 1, 2. The fitting process to obtain parameters p i (T) and N s was repeated for various stress temperatures (25, 75, 125, and 175 °C) (Fig. 5(b)). The measured ΔI DS data of 25 °C and the theoretical line of equation (5) are plotted with different pi (Fig. 7(c)). Among various fitting values, the measurement data can best be described as p 1 is 0.01 and p 2 is 0.0005. The slope of [ln(p i ) vs 1/kT] presents the energy barriers height E i for the detrapping electrons influencing on the charge flux J s (i) (i = 1, 2) in Eq. (6): E 1 = 0.17 eV, E 2 = 0.23 eV (Si3N4 gate insulator), and E 1 = 0.18 eV, E 2 = 0.27 eV (SiO2 gate insulator) (Fig. 7(d)). The available trap density (N S ) which can recapture the secondary electrons, are of the order of 109 cm−2 (Si3N4 gate insulator) and 108 cm−2 (SiO2 gate insulator), implying that most of the secondary electrons from the initial traps are not re-trapping. The N 0 and N s values of the a-IHZO TFT with Si3N4 gate insulator are each approximately one order of magnitude higher than those of the a-IHZO TFT with SiO2 gate insulator.

(a) Source to drain current of the a-IHZO TFTs with SiO2 gate insulator during the huge long pulse width (1000 s) at the gate pulse V GS of 8 V measured at various temperatures. (b) Source to drain current shift of the a-IHZO TFTs with SiO2 and Si3N4 gate insulators during the huge long pulse width (1000 s) of the pulse in Fig. 6(a). (c) Source to drain current shift with different P i during the huge long pulse width (1000 s), measured at 25 °C, of the pulse in Fig. 6(a). (d) Extracted activation energies Ei corresponding to Pi data of a-IHZO TFTs with SiO2 and Si3N4 gate insulators.

Discussion

In this study, we proposed a quantitative analysis of the dominant mechanism of device instability stemming from the charge trapping behavior and defect characteristics of oxide TFTs. To systematically analyze the charge trapping mechanism, we probed the subgap DOS by MFM measurements, as well as examining fast/slow transient charging and trap energy by short pulse stress and long pulse stress. These analyses provide a foundation for an instability model of oxide TFTs.

The obtained results show that the a-IHZO TFT with Si3N4 gate insulator is vulnerable to fast/slow charge trapping, causing significant device instability, high acceptor-like defect density, and shallow trap energy compared with those of the a-IHZO TFT with SiO2 gate insulator. We believe that this method will help to understand the defects of oxide semiconductor transistor and will guide the direction of defect control.

Methods

Device Fabrication

Molybdenum metal used as a gate/source/drain electrode was deposited by DC sputtering. For the preparation of both the Si3N4 and SiO2 gate insulators, we used plasma-enhanced chemical vapor deposition (PECVD) in the gas chemistry of SiH4/NH3 and SiH4/N2O, respectively. Then, a-IHZO oxide semiconductor films of thickness 40 nm were deposited by means of a radio-frequency plasma sputtering method. The IHZO targets were composed of a mixture of HfO2, In2O3, and ZnO powders. For example, the IHZO (7 mol% - Hf content) target was composed of HfO2: In2O3: ZnO = 0.07: 1: 1. The a-IHZO (7 mol% - Hf content) film composition was verified by analyzing the energy dispersion spectrometry (see the Fig. 1(c)). For the comparison purpose of effect of IHZO semiconductor regarding Hf contents, the Hf content of the IHZO targets were prepared in contents of 4, 7, and 10 mol%. After the formation of the a-IHZO layer, the etch stopper layer was formed of SiO2 using PECVD. Subsequently, the TFT devices were passivated with PECVD SiO2 followed by contact etching.

Device Characterization

The DC I–V measurements were performed using a semiconductor parameter analyzer (Agilent 4156 C), and the fast I–V (FIV) and pulse I–V (PIV) measurements were carried out using a pulse-generation unit (Agilent B1104A) and a digital oscilloscope (Agilent MSO6052A). For the DC I–V measurements, the voltage sweep rate was 1 V/s, whereas for the FIV and PIV measurements, the voltage scan rate was 1 V/µs. The multi-frequency measurements (MFM) were performed using an LCR meter (Agilent 4284 A).

References

Wager, J. F. Transparent Electronics. Science 300, 1245–1246 (2003).

Granqvist, C. G. In Transparent Electronics: From Synthesis to Applications, (Eds: Facchetti, A. & Marks, T. J.) (John Wiley & Sons, Ltd 2010).

Kim, M.-G., Kanatzidis, M. G., Facchetti, A. & Marks, T. J. Low-temperature fabrication of high-performance metal oxide thin-film electronics via combustion processing. Nature Materials 10, 382–388 (2011).

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Kim, Y.-H. et al. Flexible metal-oxide devices made by room-temperature photochemical activation of sol–gel films. Nature 489, 128–132 (2012).

Jeon, S. et al. Origin of High Photoconductive Gain in Fully Transparent Heterojunction Nanocrystalline Oxide Image Sensors and Interconnects. Advanced Materials 26, 7102–7109 (2014).

Jeon, S. et al. Gated three-terminal device architecture to eliminate persistent photoconductivity in oxide semiconductor photosensor arrays. Nature Materials 11, 301–305 (2012).

Lee, E., Kim, T., Benayad, A., Hur, J., Park, G.-S. & Jeon, S. High mobility and high stability glassy metal-oxynitride materials and devices. Scientific Reports 6, 23940 (2016).

Fortunato, E., Barquinha, P. & Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. Advanced Materials 24, 2945–2986 (2012).

Lee, J.-Y., Connor, S. T., Cui, Y. & Peumans, P. Solution-Processed Metal Nanowire Mesh Transparent Electrodes. ACS Nano 8, 689–692 (2008).

Barquinha, P., Goncalves, G., Pereira, L., Martins, R. & Fortunato, E. Effect of annealing temperature on the properties of IZO films and IZO based transparent TFTs. Thin Solid Films 515, 8450–8454 (2007).

Nathan, A., Lee, S., Jeon, S. & Robertson, J. Amorphous Oxide Semiconductor TFTs for Displays and Imaging. Journal of Display Technology 10, 917–927 (2014).

Park, J. C., Kim, S. W., Kim, C. J. & Lee, H.-N. The Effects of Gadolinium Incorporation Into Indium–Zinc–Oxide Thin-Film Transistors. IEEE Electron Device Letters 33, 809–811 (2012).

Seo, D. et al. Fully transparent InGaZnO thin film transistors using indium tin oxide/graphene multilayer as source/drain electrodes. Appl. Phys. Lett. 97, 172106 (2010).

Park, J.-S. et al. Novel ZrInZnO Thin-film Transistor with Excellent Stability. Advanced Materials 21, 329–333 (2008).

Munzenrieder, N. et al. Flexible Self-Aligned Amorphous InGaZnO Thin-Film Transistors With Submicrometer Channel Length and a Transit Frequency of 135 MHz. IEEE Transaction on Electron Devices 60, 2815–2820 (2013).

Choi, H.-S. et al. Influence of Hf contents on interface state properties in a-HfInZnO thin-film transistors with SiNx/SiOx gate dielectrics. Appl. Phys. Lett. 99, 183502 (2011).

Van de Walle, C. G. Hydrogen as a cause of doping in zinc oxide. Phys. Rev. Lett. 85, 1012–1015 (2000).

Choi, H.-S. & Jeon, S. Anomalous high photoconductivity in short channel indium-zinc-oxide photo-transistors. Appl. Phys. Lett. 106, 013503 (2015).

Jeon, S. et al. Short channel device performance of amorphous InGaZnO thin film transistor. Appl. Phys. Lett. 99, 082104 (2011).

Ahn, S. et al. High-performance nanowire oxide photo‐thin film transistor. Adv. Mater. 25, 5549–5554 (2013).

Choi, H. et al. Influence of Hf contents on interface state properties in a-HfInZnO thin-film transistors with SiNx/SiOx gate dielectrics. Appl. Phys. Lett. 99, 183502 (2011).

Choi, H.-S. & Jeon, S. Field-induced macroscopic barrier model for persistent photoconductivity in nanocrystalline oxide thin-film transistors. Appl. Phys. Lett. 104, 133507 (2014).

Jeong, J. K. Photo-bias instability of metal oxide thin film transistors for advanced active matrix displays. J. Mater. Res. 28, 2071–2084 (2013).

Choi, H. The impact of active layer thickness on low-frequency noise characteristics in InZnO thin-film transistors with high mobility. Appl. Phys. Lett. 100, 173501 (2012).

Choi, H. et al. Verification of interface state properties of a-InGaZnO thin-film transistors with and gate dielectrics by low frequency noise measurements. IEEE Electron Device Lett. 32, 1083–1085 (2011).

Jeong, J. et al. Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors. Appl. Phys. Lett. 93, 123508 (2008).

Cheong, W. S. et al. Current stress induced electrical instability in transparent zinc tin oxide thin-film transistors. J. Nanosci. Nanotechnology 12, 3421–3424 (2012).

Kim, T., Nam, Y., Hur, J., Park, S.-H. K. & Jeon, S. The influence of hydrogen on defects of In-Ga-Zn-O semiconductor thin-film transistors with atomic-layer deposition of Al2O3. IEEE Electron Device Lett. 37, 1131–1134 (2016).

Ramon, M. E., Akyol, T., Shahrjerdi, D., Young, C. D., Cheng, J., Register, L. F. & Banerjee, S. K. Fast and slow transient charging in various III-V field-effect transistors with atomic-layer-deposited-Al2O3 gate dielectric. Appl. Phys. Lett. 102, 022104 (2013).

Jung, U., Lee, Y. G., Kang, C. G., Lee, S., Kim, J. J., Hwang, H. J., Lim, S. K., Ham, M.-H. & Lee, B. H. Quantitatively estimating defects in graphene devices using discharge current analysis method. Scientific Reports 4, 4886 (2014).

Lee, S. et al. Extraction of subgap density of states in amorphous InGaZnO thin-film transistors by using multifrequency capacitance–voltage characteristics. IEEE Electron Device Letters 31, 231–233 (2010).

Young, C. D. et al. Ultra-short pulse current–voltage characterization of the intrinsic characteristics of high-k devices. Japan. J. Appl. Phys. 44, 2437–2440 (2005).

Shen, C. et al. A fast measurement technique of MOSFET Id–Vg characteristics. IEEE Electron Device Lett. 27, 55–57 (2006).

Heh, D., Young, C. D. & Bersuker, G. Experimental evidence of the fast and slow charge trapping/detrapping processes in high-k dielectrics subjected to PBTI stress. IEEE Electron Device Lett 29, 180–182 (2008).

Young, C. D. et al. Pulsed–methodology and its application to electron trapping characterization and defect density profiling. IEEE Trans. Electron. Device Lett. 56, 1322–1329 (2009).

Young, C. D. et al. The pulsed Id–Vg methodology and its application to the electron trapping characterization of high-k gate dielectrics. J. Semicond. Technol. Sci. 10, 79–99 (2010).

Kim, T., Hur, J. & Jeon, S. The influence of interfacial defects on fast charge trapping in nanocrystalline oxide-semiconductor thin film transistors. Semicond. Sci. Technol. 31, 055014 (2016).

Kim, T., Hur, J. & Jeon, S. Pulse I-V characterization of a nanocrystalline oxide device with sub-gap density of states. Nanotechnology 27, 215203 (2016).

Kim, T., Hur, J. & Jeon, S. Fast transient charging behavior of HfInZnO thin-film transistor. Appl. Phys. Lett. 107, 093503 (2015).

Kim, T., Nam, Y., Hur, J., Park, S.-H. K. & Jeon, S. Effect of hydrogen on dynamic charge transport in amorphous oxide thin film transistors. Nanotechnology 27, 325203 (2016).

Kim, T., Choi, R. & Jeon, S. Influence of fast charging on accuracy of mobility in a-InHfZnO thin-film transistor. IEEE Electron Device 38, 203–206 (2017).

Bersuker, G. et al. Mechanism of Electron Trapping and Characteristics of Traps in HfO2 Gate Stacks. IEEE Trans. Dev. Mat. Reliability 7, 138–145 (2007).

Kamiya, T. & Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2, 15–22 (2010).

Kamiya, T., Nomura, K. & Hosono, H. Electronic Structures Above Mobility Edges in Crystalline and Amorphous In-Ga-Zn-O: Percolation Conduction Examined by Analytical Model. Journal of Display Technology 5, 462–467 (2009).

Chen, C., Abe, K., Kumomi, H. & Kanicki, J. Density of states of a-InGaZnO from temperature-dependent field-effect studies. IEEE Trans. Electron Devices 56, 1177–1183 (2009).

Sim, J. H. et al. Trapping/de-trapping gate bias dependence of Hf-silicate dielectrics with poly and TiN gate electrode. Jpn. J. Appl. Phys. 44, 2420–2423 (2005).

Heh, D., Choi, R., Young, C. D. & Bersuker, G. Fast and slow charge trapping/detrapping processes in high-κ nMOSFETs. in Proc. IEEE IRW Final Report 120–124 (2006).

Acknowledgements

This research was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by Korea Government (No. 2015M3A7B7045496 and No. 2017R1A2A2A05022574) as well as the Technology Innovation Program (No. 10049163) funded by the Ministry of Trade, Industry and Energy (MOTIE, Korea).

Author information

Authors and Affiliations

Contributions

T.K. and S.J. contributed equally to this work. S.J. designed this work. S.P. and S.J. carried out the a-IHZO TFTs fabrication and T.K. performed AC device characterization. T.K. and S.J. wrote the manuscript. All authors reviewed the results and implications and commented on the manuscript at all stages. The project was guided by S.J.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kim, T., Park, S. & Jeon, S. Fast and slow transient charging of Oxide Semiconductor Transistors. Sci Rep 7, 11850 (2017). https://doi.org/10.1038/s41598-017-12155-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-12155-3

This article is cited by

-

Improvement of flicker phenomenon at low frequencies in AMOLED displays by applying compensation scheme of variable reset voltage

Scientific Reports (2025)

-

Analytical modeling and experimental characterization of drift in electrolyte-gated graphene field-effect transistors

npj 2D Materials and Applications (2025)