Abstract

An optimized millimeter-wave digital controlled oscillator (DCO) in a 40-nm CMOS process is presented in this work. The coarse-tuning modules and medium-tuning modules of the DCO utilize modified binary-weighted digitally controlled transmission lines (DCTLs) to achieve a better compromise among smaller chip size, higher resonant frequency, better tuning resolution and lower phase noise. The tuning precision and die size of the medium tuning bank are improved without changing the binary coding rules by replacing the lowest-weight bit of the DCTLs with switched capacitors. In comparison with traditional DCTLs, the control bits of the coarse and medium tuning modules have been changed from 30 to 8, resulting in a 34.4% reduction in overall length (from 122\(\upmu\)m to 80\(\upmu\)m). In addition, the DCO’s fine-tuning modules are achieved using a binary-weighted switched capacitors array connected to the secondary winding of a low-coupling transformer, which enhances the DCO’s fine-tuning bank for better frequency resolution with less circuit complexity. The measured tuning range of the optimized DCO is 76-81GHz with a smaller die size of 0.12mm\(^2\). This results in an outstanding figure of merit (\(FoM_A\)) of − 190.52dBc/Hz.

Similar content being viewed by others

Introduction

Digital phase-locked loop (DPLL) has been gradually adopted in millimeter-wave communication systems due to its higher level of integration, more flexible configurability, and process portability. The DCO is a key component of DPLL system. However, due to the limitations in frequency resolution, tuning range, and circuit complexity at higher millimeter-wave frequency bands, the design of DCO remains challenging in building DPLL systems.

Much research has been done over the last decade to extend the tuning range of oscillators. Tuning range extension can be achieved by increasing the number of switches and the capacitance in the inductor output legs1\(^,\)2. However, more switched capacitors will result in increased area consumption and non-linearity. Due to the additional losses introduced, the DCO may suffer from phase noise degradation and increased power dissipation to meet the start-up conditions3\(^,\)4.

Alternatively, DCTLs are used in the DCO’s tuning banks for higher Q and lower substrate loss5\(^,\)6. However, conventional DCTLs always generate a lot of parasitic capacitances due to their large die size, which will break the trade-off among the phase noise, tuning range and resonant frequency of the DCO7\(^,\)8. The frequency resolution of the DCO with a capacitive source degeneration coupling circuit topology is often affected by the transconductance of the cross-coupled transistor pair9. Although the switched capacitor based tuning banks can achieve a higher frequency resolution, the utilization of a significant number of capacitors also degrades the phase noise performance of the DCO10\(^,\)11. Thus, it remains a challenging task to modify the resonant tank of the millimeter-wave DCO to improve the phase noise, resonant frequency, frequency resolution and die size trade-off.

As shown in Fig. 1, The optimized DCO is integrated into an E-band DPLL. The reference phase accumulator (RPA), the variable phase accumulator (VPA), the time-to-digital converter (TDC), and the phase error detector are used for phase detection, which is similar to the phase frequency detector in a charge pump phase-locked loop. The object of quantization is the difference between VPA and TDC. The integer phase of CKV, divided clock of the DCO output frequency, is quantized by the VPA, while the difference of the fractional phase between CKV and \(f_{ref}\) is quantized by the TDC. Since the generation of the fractional modulation in the DPLL loop results from the combination of other modules, further improvement of the DPLL resolution does not place significant demands on the resolution of the mm-wave DCO.

This paper presents a millimeter-wave DCO that offers a trade-off among die size, resonant frequency and phase noise. The hybrid tuning banks are described separately in subsequent section. Eventually, the experimental results demonstrate the expected characteristics of the proposed circuits.

Design and implementation of the circuit

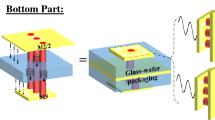

Figure 2 shows the circuit topology of the E-band DCO, consisting of coarse tuning bank (CB), medium tuning bank (MB) and fine tuning bank (FB). The CB is based on 4-bit modified binary-weighted DCTLs, while MB consists of 3-bit modified binary-weighted DCTLs and 1-bit switched capacitor. Additionally, the FB is composed of a 4-bit switched capacitor array connected to the secondary coil of a low-coupling transformer.

Coarse & medium tuning modules

The equivalent schematic of CB and MB based on binary-weighted DCTLs is illustrated in Fig. 3. Since the proposed DCTLs change the number of capacitors connected to the tuning bank by changing the effective dielectric constant via MOS switches, this operation controls the resonant frequency at discrete frequency points according to different control codes12. With CM or MB connected to the circuit by the MOSFET switches, the characteristic impedance is calculated as

Where \(L_0\) is the equivalent inductance of the transmission lines’ per unit length, \(C_0\) is the coupling capacity between two parallel transmission lines and the capacitive coupling between the transmission lines and the substrate. \(C_M\) is the Metal-Insulator-Metal capacitance between the floating strips and the transmission lines.

As shown in Fig.4, unlike the traditional thermometer-coded DCTLs, the floating strips used in these modified DCTLs are selectively optimized rather than strictly binary-weighted, resulting in the most linear effective dielectric constant to overcome the non-linearity problem. The CB based on the proposed DCTLs achieves a total reduction in length of 31.8% (from 91\(\upmu\)m and 62\(\upmu\)m). Similarly, the control bits of the MB (excluding the lowest weight control bit of the MB consisting of the switched capacitors) are reduced from 15 to 4, achieving a 41.9% length reduction (from 31\(\upmu\)m to 18\(\upmu\)m). The passive component loss and the fixed parasitic capacitance are reduced, while the overall Q-factor of the proposed DCTLs is increased (Q=14\(\sim\) 16 @78GHz).

Figure 5 displays the structure of the hybrid modified binary-weighted DCTLs based MB. The switch capacitors are used as the lowest weight bit of the medium-tuning precision control codes, which overcomes the tuning precision limit of the DCTLs-only tuning modules without changing the binary encoding rules. At the same time, this technique reduces the die size of the MB and the impact of parasitic devices on circuit performance.

Table 1 demonstrates the comparison of the control bits between the thermometer-coded DCTLs and the proposed DCTLs applied in the CB. The tuning modules utilizing modified binary-weighted DCTLs can achieve a high resonant frequency and broad frequency tuning range with a reduced number of control bits, resulting in a more condensed chip size.

Fine tuning module

The simplified equivalent schematic of the FB and the low coupling coefficient transformer is shown in Fig. 6. The FB is achieved by using an array of binary capacitors connected to the secondary coil of the transformer to promote frequency resolution while reducing circuit complexity, as opposed to the typical Class F VCOs that focus primarily on enhancing the third harmonic and extending the tuning range13,14,15,16.

The rate of change of \(L_{eq}\) with the respect to the equivalent capacitance \(C_L\) of the FB can be expressed as

Where k is the coupling factor of the transformer. \(L_{p}\) and \(L_{s}\) are the respective inductances of the coils of the transformer.

The design of the transformer is a crucial part of the overall DCO and particular attention should be paid to the coupling coefficient and the Q-factor. The lower coupling coefficient k allows \(L_{eq}\) to increase smoothly and linearly with the increase in \(C_L\), as shown in equation (2). Figure 7 shows that the Q of the two transformer coils at the operating frequency is above 15 and the coupling factor of the transformer is below 0.25. To minimize the frequency tuning step, the coupling coefficient of the transformer k is set to 0.21. In addition, the detrimental effects of parasitic capacitance in the tuning bank can also be reduced by using a coupled transformer with such a small k17,18,19. The binary-weighted array of switched capacitors connected to the transformer’s secondary coil can be used to achieve smaller fine-tuning steps. Figure 8 shows that when the equivalent capacitance of the switched capacitor array (\(C_L\)) is between 12fF and 23fF and the equivalent parallel resistance (\(R_L\)) is between 560\(\Omega\) and 2200\(\Omega\), the corresponding equivalent tank inductance (\(L_{eq}\)) is between 49.28pH and 49.38pH. This means that a large variation in \(C_L\) is converted into a small variation in the inductance of \(L_{eq}\) by the transformer coupling technique.

Measurements

The optimized DCO was integrated into an E-band DPLL and fabricated on a 40 nm CMOS process as shown in Fig. 9. As shown in Fig. 10, the performances of the DCO were measured using high frequency GSG probes, spectrum analyzer and phase noise analyzer. The die area of the DCO core is 0.48mm\(\times\)0.25mm.

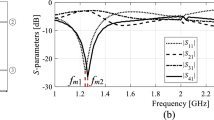

The medium-tuning curves measured under various coarse tuning codes are displayed in Fig. 11. The CB implemented by the modified binary-weighted DCTLs corresponds to 16 discrete frequency points. The average step size of the coarse-tuning can reach 297 MHz/bit, while the average step size of the medium-tuning can reach 17 MHz/bit. When the control codes of the CB are the lowest, the tuning range of the MB is 80.5-81.03GHz (530MHz), which can fully cover the maximum coarse-tuning step. Figure 12(a) shows the measured fine-tuning characteristic. If the control codes of both the MB and CB are at lowest, steps from 2 to 7 MHz can be achieved for frequency tuning. But with the control codes of the CB at 16 and the MB at 32, the frequency tuning step is from 2 and 6MHz. This means that a continuous tuning range of 76.23-76.29 GHz (60 MHz) can be achieved in the lowest frequency band, which fully covers the largest medium-tuning step size.Figure 12(b) shows the measured differential non-linearity (DNL) of the CB and MB of the DCO. A total of 8 chips were tested, of which 5 chips gave the consistent results. While the control code of the FB remains constant, the measured DNL is -0.45 LSB in the worst case among 5 chips.

Figure 13 exhibits the measured results of the DCO’s spectrum and phase noise spectrum. The DCO is tuned to oscillate at 76-81 GHz. The phase noise of the output signal at 10MHz offset is − 116.72dBc/Hz at 77GHz. The power dissipated of the DCO core is approximately 21.5mW at 0.9V supply voltage. The hump in the phase noise curve is caused by the up-conversion of the power supply noise by the DCO’s the cross-coupled amplifier, which creates multi-frequency peaks near the oscillation frequency. The DCO achieves the required metrics for the DPLL system and is able to meet the system requirements.

The proposed DCTLs result in a 34.4\(\%\) reduction in the overall length of the CB and MB, while maintaining a high Q-factor (14\(\sim\)16 @78GHz), suggesting that it is not necessary to increase the inductor size excessively to prevent phase noise degradation of the resonant tank. As a result, the die area of the proposed DCO is reduced to some extent. Table 2 shows that the above features help to achieve an excellent balance between die size, phase noise, frequency resolution and resonant frequency, resulting in exceptional FoM and \(FoM_A\)20, especially in terms of die area.

Conclusion

A millimeter-wave DCO has been fabricated on a 40-nm CMOS process, featuring a trade-off among chip size, phase noise, frequency resolution, and resonant frequency. The MB and CB, which are based on binary-weighted DCTLs, and the FB, which is a binary-weighted switched capacitor array connected to the secondary winding of a low-coupling transformer, are integrated into the DCO’s resonance tank. The modified DCO reaches a high \(FoM_A\) of -190.52dBc/Hz with a resonant frequency range from 76 to 81GHz, while the frequency resolution is 2MHz.

Data availability

The data that support the findings of this study are available from the corresponding author L.T., upon reasonable request.

References

Savoj, J. et al. A wide common-mode fully-adaptive multi-standard 12.5gb/s backplane transceiver in 28nm cmos. In 2012 Symposium on VLSI Circuits (VLSIC), 104–105, https://doi.org/10.1109/VLSIC.2012.6243811 (2012).

Hong, F., Zhang, H. & Zhao, D. An x-band cmos vco using ultra-wideband dual common-mode resonance technique. IEEE Trans. Circuits Syst. I Regul. Pap. 69, 3579–3590. https://doi.org/10.1109/TCSI.2022.3181139 (2022).

Yagi, M., Komoku, K., Morishita, T. & Itoh, N. A study on 14 bit digital controlled oscillator using switched striped inductor. In 2019 IEEE Asia-Pacific Microwave Conference (APMC), 847–849 (2019).

Lin, C.-M., Lin, Y.-T., Kao, K.-Y. & Lin, K.-Y. A dual-band cmos standing-wave digitally controlled oscillator for automotive radars. In 2019 IEEE MTT-S International Microwave Symposium (IMS), 385–388 (IEEE, 2019).

Mostafa, P. & Chatterjee, S. A ditherless 2.4 ghz high resolution lc dco. In 2019 2nd International Conference on Innovations in Electronics, Signal Processing and Communication (IESC), 279–282 (IEEE, 2019).

Xu, N., Rhee, W. & Wang, Z. A 2 ghz 2 mb/s semi-digital \(2^+\)-point modulator with separate fir-embedded 1-bit dco modulation in 0.18\(\mu\)m cmos. IEEE Microwave Wirel. Components Lett. 25, 253–255 (2015).

Ullah, F., Liu, Y., Wang, X., Sarfraz, M. M. & Zhang, H. Bandwidth-enhanced differential vco and varactor-coupled quadrature vco for mmwave applications. AEU-Int. J. Electron. Commun. 95, 59–68 (2018).

Hussein, A. I., Vasadi, S. & Paramesh, J. A 50–66-ghz phase-___domain digital frequency synthesizer with low phase noise and low fractional spurs. IEEE J. Solid-State Circuits 52, 3329–3347 (2017).

Hong, C.-H., Wu, C.-Y. & Liao, Y.-T. Robustness enhancement of a class-c quadrature oscillator using capacitive source degeneration coupling. IEEE Trans. Circuits Syst. II Express Briefs 62, 16–20 (2014).

Huang, Z. & Luong, H. C. Design and analysis of millimeter-wave digitally controlled oscillators with c-2c exponentially scaling switched-capacitor ladder. IEEE Trans. Circuits Syst. I Regul. Pap. 64, 1299–1307 (2017).

Tsai, C.-H. et al. Analysis of a 28-nm cmos fast-lock bang-bang digital pll with 220-fs rms jitter for millimeter-wave communication. IEEE J. Solid-State Circuits 55, 1854–1863 (2020).

Murphy, D. et al. A low phase noise, wideband and compact cmos pll for use in a heterodyne 802.15. 3c transceiver. IEEE J. Solid-State Circ. 46, 1606–1617 (2011).

Guo, H., Chen, Y., Huang, Y., Mak, P.-I. & Martins, R. P. 8.4 an 83.3-to-104.7ghz harmonic-extraction vco incorporating multi-resonance, multi-core, and multi-mode (3m) techniques achieving -124dbc/hz absolute pn and 190.7dbc/hz \(\text{FoM}_{\rm t}\). In 2023 IEEE International Solid-State Circuits Conference (ISSCC), 152–154, https://doi.org/10.1109/ISSCC42615.2023.10067832 (2023).

Guo, H., Chen, Y., Mak, P.-I. & Martins, R. P. 20.1 a 5.0-to-6.36ghz wideband-harmonic-shaping vco achieving 196.9dbc/hz peak fom and 90-to-180khz 1/f3 pn corner without harmonic tuning. In 2021 IEEE International Solid-State Circuits Conference (ISSCC), vol. 64, 294–296, https://doi.org/10.1109/ISSCC42613.2021.9365761 (2021).

Babaie, M. & Staszewski, R. B. An ultra-low phase noise class-f 2 cmos oscillator with 191 dbc/hz fom and long-term reliability. IEEE J. Solid-State Circuits 50, 679–692. https://doi.org/10.1109/JSSC.2014.2379265 (2015).

Wu, W., Long, J. R. & Staszewski, R. B. High-resolution millimeter-wave digitally controlled oscillators with reconfigurable passive resonators. IEEE J. Solid-State Circuits 48, 2785–2794. https://doi.org/10.1109/JSSC.2013.2282701 (2013).

Ambulker, S. & Nakhate, S. Wide tuning range low phase noise vco for v-band application. IET Microwaves Antennas Propag. 12, 756–764 (2018).

Basaligheh, A., Saffari, P., Winkler, W. & Moez, K. A wide tuning range, low phase noise, and area efficient dual-band millimeter-wave cmos vco based on switching cores. IEEE Trans. Circuits Syst. I Regul. Pap. 66, 2888–2897 (2019).

Yu, S.-A. & Kinget, P. R. Scaling \(lc\) oscillators in nanometer cmos technologies to a smaller area but with constant performance. IEEE Trans. Circuits Syst. II Express Briefs 56, 354–358 (2009).

Li, C., Guo, J., Qin, P. & Xue, Q. A wideband mode-switching quad-core vco using compact multi-mode magnetically coupled lc network. IEEE J. Solid-State Circuits 58, 1959–1972. https://doi.org/10.1109/JSSC.2023.3235347 (2023).

Zong, Z., Chen, P. & Staszewski, R. B. A low-noise fractional- \({N}\) digital frequency synthesizer with implicit frequency tripling for mm-wave applications. IEEE J. Solid-State Circuits 54, 755–767. https://doi.org/10.1109/JSSC.2018.2883397 (2019).

Bourdel, S. et al. 77.8 ghz standing-wave oscillator based on a tuneable slow-wave coplanar stripline resonator. In 2020 18th IEEE International New Circuits and Systems Conference (NEWCAS), 18–21, https://doi.org/10.1109/NEWCAS49341.2020.9159799 (2020).

Sharma, E. et al. Design of a 77-ghz lc-vco with a slow-wave coplanar stripline-based inductor. IEEE Trans. Circuits Syst. I Regul. Pap. 67, 378–388. https://doi.org/10.1109/TCSI.2019.2926415 (2020).

Welp, B. et al. Versatile dual-receiver 94-ghz fmcw radar system with high output power and 26-ghz tuning range for high distance applications. IEEE Trans. Microw. Theory Tech. 68, 1195–1211. https://doi.org/10.1109/TMTT.2019.2955127 (2020).

Acknowledgements

This work is supported by the National Natural Science Foundation of China (No. 62234012).

Author information

Authors and Affiliations

Contributions

L.T. presented the theoretical analysis. S.X. and L.T. conceived the experiments. Y.L. and Y.Z. conducted the experiments. Z.J. and X.T. performed statistical analysis and figure generation. Z.Y. conducted the experiments and contacted the funding. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tang, L., Yu, Z., Lu, Y. et al. An optimized DCO with modified binary-weighted DCTLs based hybrid tuning banks for an E-band DPLL. Sci Rep 14, 944 (2024). https://doi.org/10.1038/s41598-024-51510-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-51510-z

This article is cited by

-

High-Performance Low-Power Digital Oscillator Using CMOS Technology

Transactions on Electrical and Electronic Materials (2025)