Abstract

Federated learning provides a framework for multiple participants to collectively train a neural network while maintaining data privacy, and is commonly achieved through homomorphic encryption. However, implementation of this approach at a local edge requires key generation, error polynomial generation and extensive computation, resulting in substantial time and energy consumption. Here, we report a memristor compute-in-memory chip architecture with an in situ physical unclonable function for key generation and an in situ true random number generator for error polynomial generation. Our architecture—which includes a competing-forming array operation method, a compute-in-memory based entropy extraction circuit design and a redundant residue number system-based encoding scheme—allows low error-rate computation, the physical unclonable function and the true random number generator to be implemented within the same memristor array and peripheral circuits. To illustrate the functionality of this memristor-based federated learning, we conduct a case study in which four participants cotrain a two-layered long short-term memory network with 482 weights for sepsis prediction. The test accuracy on the 128-kb memristor array is only 0.12% lower than that achieved with software centralized learning. Our approach also exhibits reduced energy and time consumption compared with conventional digital federated learning.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

27,99 € / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

118,99 € per year

only 9,92 € per issue

Buy this article

- Purchase on SpringerLink

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The datasets that we used for benchmark are publicly available. The source data of Figs. 2c–e, 3f–h and 4c–f, Extended Data Figs. 2c–g and 3 and Supplementary Figs. 1, 2 and 4 are available via GitHub at https://github.com/Tsinghua-LEMON-Lab/Memeristor_based_Federated_Learning. Source data are provided with this paper. Additional data supporting the findings of this study are available from the corresponding authors upon reasonable request.

Code availability

The codes that support the findings of this study are available via GitHub at https://github.com/Tsinghua-LEMON-Lab/Memeristor_based_Federated_Learning. Additional codes are available from the corresponding authors upon reasonable request.

References

Warnat-Herresthal, S. et al. Swarm learning for decentralized and confidential clinical machine learning. Nature 594, 265–270 (2021).

Froelicher, D. et al. Truly privacy-preserving federated analytics for precision medicine with multiparty homomorphic encryption. Nat. Commun. 12, 5910 (2021).

Annas, G. J. HIPAA regulations: a new era of medical-record privacy? N. Engl. J. Med. 348, 1486 (2003).

Voigt, P. & Von dem Bussche, A. The EU General Data Protection Regulation (GDPR). A Practical Guide 1st edn (Springer, 2017).

Rieke, N. et al. The future of digital health with federated learning. NPJ Digital Med. 3, 119 (2020).

Nguyen, D. C. et al. Federated learning for smart healthcare: a survey. ACM Comput. Surv. 55, 60 (2022).

Xu, J. et al. Federated learning for healthcare informatics. J. Healthc. Inform. Res. 5, 1–19 (2021).

Sarkar, E. et al. Privacy-preserving cancer type prediction with homomorphic encryption. Sci. Rep. 13, 1661 (2023).

Dayan, I. et al. Federated learning for predicting clinical outcomes in patients with COVID-19. Nat. Med. 27, 1735–1743 (2021).

Pati, S. et al. Federated learning enables big data for rare cancer boundary detection. Nat. Commun. 13, 7346 (2022).

Bai, X. et al. Advancing COVID-19 diagnosis with privacy-preserving collaboration in artificial intelligence. Nat. Mach. Intell. 3, 1081–1089 (2021).

Wu, C. et al. A federated graph neural network framework for privacy-preserving personalization. Nat. Commun. 13, 3091 (2022).

Khalil, K. et al. A federated learning model based on hardware acceleration for the early detection of Alzheimer’s disease. Sensors 23, 8272 (2023).

Fan, J. & Vercauteren, F. Somewhat practical fully homomorphic encryption. Cryptology ePrint Archive Paper 2012/144, https://eprint.iacr.org/2012/144 (2012).

Lin, Y. et al. Uncertainty quantification via a memristor Bayesian deep neural network for risk-sensitive reinforcement learning. Nat. Mach. Intell. 5, 714–723 (2023).

Zhang, W. et al. Edge learning using a fully integrated neuro-inspired memristor chip. Science 381, 1205–1211 (2023).

Ambrogio, S. et al. An analog-AI chip for energy-efficient speech recognition and transcription. Nature 620, 768–775 (2023).

Hung, J.-M. et al. A four-megabit compute-in-memory macro with eight-bit precision based on CMOS and resistive random-access memory for AI edge devices. Nat. Electron. 4, 921–930 (2021).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Modha, D. S. et al. Neural inference at the frontier of energy, space, and time. Science 382, 329–335 (2023).

Aguirre, F. et al. Hardware implementation of memristor-based artificial neural networks. Nat. Commun. 15, 1974 (2024).

Harabi, K.-E. et al. A memristor-based Bayesian machine. Nat. Electron. 6, 52–63 (2023).

Bonnet, D. et al. Bringing uncertainty quantification to the extreme-edge with memristor-based Bayesian neural networks. Nat. Commun. 14, 7530 (2023).

Meng, F.-H. & Lu, W. D. Compute-in-memory technologies for deep learning acceleration. IEEE Nanotechnol. Mag. 18, 44–52 (2024).

Wu, Y. et al. Bulk-switching memristor-based compute-in-memory module for deep neural network training. Adv. Mater. 35, 2305465 (2023).

Huang, Y., Ravichandran, V., Zhao, W. & Xia, Q. Towards energy-efficient computing hardware based on memristive nanodevices. IEEE Nanotechnol. Mag. 17, 30–38 (2023).

Zhao, H. et al. Energy-efficient high-fidelity image reconstruction with memristor arrays for medical diagnosis. Nat. Commun. 14, 2276 (2023).

Wang, C. et al. Parallel in-memory wireless computing. Nat. Electron. 6, 381–389 (2023).

Zhao, H. et al. Implementation of discrete Fourier transform using RRAM arrays with quasi-analog mapping for high-fidelity medical image reconstruction. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 12.4.1–12.4.4 (IEEE, 2021).

Salamat, S., Imani, M., Gupta, S. & Rosing, T. Rnsnet: in-memory neural network acceleration using residue number system. In Proc. 2018 IEEE International Conference on Rebooting Computing (ICRC) 1–12 (IEEE, 2018).

Roohi, A., Taheri, M., Angizi, S. & Fan, D. Rnsim: Efficient deep neural network accelerator using residue number systems. In Proc. 2021 IEEE/ACM International Conference On Computer Aided Design (ICCAD) 1–9 (IEEE, 2021).

Haron, N. Z., Hamdioui, S. & Ahyadi, Z. ECC design for fault-tolerant crossbar memories: a case study. In Proc. 2010 5th International Design and Test Workshop 61–66 (IEEE, 2010).

Gao, Y., Al-Sarawi, S. F. & Abbott, D. Physical unclonable functions. Nat. Electron. 3, 81–91 (2020).

Nili, H. et al. Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors. Nat. Electron. 1, 197–202 (2018).

Lin, B. et al. A highly reliable RRAM physically unclonable function utilizing post-process randomness source. IEEE J. Solid-State Circuits 56, 1641–1650 (2021).

Gao, B. et al. A unified PUF and TRNG design based on 40-nm RRAM with high entropy and robustness for IoT security. IEEE Trans. Electron Devices 69, 536–542 (2022).

Chiu, Y.-C. et al. A CMOS-integrated spintronic compute-in-memory macro for secure AI edge devices. Nat. Electron. 6, 534–543 (2023).

Balatti, S., Ambrogio, S., Wang, Z. & Ielmini, D. True random number generation by variability of resistive switching in oxide-based devices. IEEE J. Emerg. Sel. Top. Circuits Syst. 5, 214–221 (2015).

Rao, M. et al. Thousands of conductance levels in memristors integrated on CMOS. Nature 615, 823–829 (2023).

Song, W. et al. Programming memristor arrays with arbitrarily high precision for analog computing. Science 383, 903–910 (2024).

Milo, V. et al. Multilevel HfO2-based RRAM devices for low-power neuromorphic networks. APL Mater. 7, 081120 (2019).

Sokolov, A. S., Abbas, H., Abbas, Y. & Choi, C. Towards engineering in memristors for emerging memory and neuromorphic computing: a review. J. Semicond. 42, 013101 (2021).

Chen, J., Li, J., Li, Y. & Miao, X. Multiply accumulate operations in memristor crossbar arrays for analog computing. J. Semicond. 42, 013104 (2021).

Garner, H. L. The residue number system. In Papers presented at the March 3–5, Western Joint Computer Conference 146–153 (1959).

Chang, C.-H., Molahosseini, A. S., Zarandi, A. A. E. & Tay, T. F. Residue number systems: a new paradigm to datapath optimization for low-power and high-performance digital signal processing applications. IEEE Circuits Syst. Mag. 15, 26–44 (2015).

Ma, J., Naas, S. A., Sigg, S. & Lyu, X. Privacy-preserving federated learning based on multi-key homomorphic encryption. Int. J. Intell. Syst. 37, 5880–5901 (2022).

Brakerski, Z. Fully homomorphic encryption without modulus switching from classical GapSVP. In Proc. Annual Cryptology Conference 868–886 (Springer, 2012).

Johnson, A. E. et al. MIMIC-III, a freely accessible critical care database. Sci. Data 3, 160035 (2016).

Wu, W. et al. A methodology to improve linearity of analog RRAM for neuromorphic computing. In Proc. 2018 IEEE symposium on VLSI technology 103–104 (IEEE, 2018).

Zhang, W. et al. Design guidelines of RRAM based neural-processing-unit: a joint device-circuit-algorithm analysis. In Proc. 56th Annual Design Automation Conference 1–6 (2019).

Li, M., Geng, H., Niemier, M. & Hu, X. S. Accelerating polynomial modular multiplication with crossbar-based compute-in-memory. In Proc. 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD) 1–9 (IEEE, 2023).

Oh, D.-R. et al. An 8-bit 1-GS/s asynchronous loop-unrolled SAR-flash ADC with complementary dynamic amplifiers in 28-nm CMOS. IEEE J. Solid-State Circuits 56, 1216–1226 (2020).

O’Halloran, M. & Sarpeshkar, R. A 10-nW 12-bit accurate analog storage cell with 10-aA leakage. IEEE J. Solid-State Circuits 39, 1985–1996 (2004).

Yao, P. et al. Fully hardware-implemented memristor convolutional neural network. Nature 577, 641–646 (2020).

Yang, K. et al. 16.3 A 23 Mb/s 23 pJ/b fully synthesized true-random-number generator in 28 nm and 65 nm CMOS. In Proc. 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) 280–281 (IEEE, 2014).

Acknowledgements

This work is supported in part by the STI 2030-Major Projects (grant no. 2021ZD0201200, H.W.), the National Natural Science Foundation of China (grant nos. 62495100 to H.W., 62025111 to H.W., 92464302 to B.G. and 624B2078 to X.L.), the Tsinghua IDG/McGovern ‘Brain+X’ Seed Grant Doctoral and Postdoctoral Program (X.L.), the Shanghai Municipal Science and Technology Major Project (H.W.), the Beijing Advanced Innovation Center for Integrated Circuits and the IoT Intelligent Microsystem Center of Tsinghua University-China Mobile Communications Group Co., Ltd Joint Institute.

Author information

Authors and Affiliations

Contributions

X.L. contributed to the overall experiment design and the writing of the paper. B.G., J.T., X.Y., H.Q. and H.W. contributed to the memristor fabrication process development. Q.Q., P.Y. and Z.H. designed the memristor circuits and built the test board. P.Y., J.L. and C.L. contributed to the benchmark of the system performance. Z.H. and J.X. helped with data analysis. Q.Z., Y.L., D.K., J.Y. and Y.N. worked on the finding of demonstration scenes and the development of AI models. B.G., X.Y. and H.W. supervised this project. All authors discussed the results and reviewed the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Kasem Khalil and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

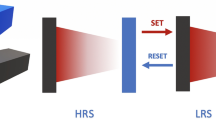

Extended Data Fig. 1 The test platform, the chip and the memristor device.

a, Photography of the test board of the 128Kb memristor chip. The test board is mounted on the V93000 test platform for controlling and testing the chip. b, The optical photograph of the 130 nm 128Kb memristors chip. The floorplan of the chip, including the digital control core and the analog crossbar core. c, The floorplan of the analogue crossbar core, including the array, BL/WL/SL drivers, SL read current paths, and BL/WL/SL voltage multiplexers. d, Transmission electron microscope (TEM) image of memristor array. e, Transmission electron microscope (TEM) image of memristor device.

Extended Data Fig. 2 The circuit design of the proposed CIM-based TRNG entropy extraction circuit.

a, The proposed CIM-based TRNG entropy extraction circuit design and working principle. In the CPTIN architecture, the same memristor cell serves as both the TRNG entropy source and the CIM computation unit. In CIM, the memristor cell may store a bit value of 1 or 0, which means that its resistance can be quite high or quite low. To adapt to this situation, we have set two charging capacitors, C1 and C2. When the resistance of the memristor is high, we connect a smaller charging capacitor C1; conversely, when the resistance is low, we switch to a larger charging capacitor C2. This ensures that the entropy extraction circuit can generate random numbers regardless of the memristor resistance. The circuit parameters are set as follows: C1 = 7fF, C1 = 500fF, VREAD = 200 mV and VTRNG_REF = 170 mV. b, Formula for calculating the theoretical output value of the TRNG. c-e, The TRNG simulation results for low resistance devices. The read resistance variation (c). The read resistance distribution of 10 randomly selected devices; a normal distribution was fitted to the results of 1000 read cycles, the curves represent the fitted results, and the horizontal line represents the mean of the normal distribution fit. (d). The corresponding TRNG output simulated by Cadence. (e). f-h, The TRNG simulation results for high resistance devices.

Extended Data Fig. 3 Supplementary Figure 7. The reliability of the 4-client federated learning.

In memristor-based federated learning, errors occur during the memristor-based encryption and decryption computations with a computational error rate of \(x\). The error rate of memristor computation leads to an error rate in the weight gradient \(\Delta W\) for weight updating. For an individual user in federated learning, the encryption and decryption computations increase the error rate of \(\Delta W\) to \({1-(1-x)}^{2}\). For a 4-client federated learning process, the total error rate of \(\Delta W\) will theoretically reach \({1-(1-x)}^{8}\). In our experiment, the computational error rate (\(x\)) is measured to be 2.24%, and the theoretical total error rate of \(\Delta W\) is 17.7%. a-f, The simulated network performance under the total error rate of \(\Delta W\). The simulation experiment was repeated 50 times for each test point using different random seeds. In the figure, the red curve indicates the average of the 50 experiment results. The bounds of the box indicate the interquartile range, and the whiskers extend to the maximum and minimum non-outlier values within 1.5 times the interquartile range. MCC, Matthews Correlation Coefficient; ROC, Receiver Operating Characteristic.

Supplementary information

Supplementary Information

Supplementary Notes 1 and 2 and Figs. 1–5.

Source data

Source Data Fig. 2

Source data for Fig. 2c–e.

Source Data Fig. 3

Source data for Fig. 3f–h.

Source Data Fig. 4

Source data for Fig. 4c–f.

Source Data Extended Data Fig. 2

Source data for Extended Data Fig. 2c–g.

Source Data Extended Data Fig. 3

Source data for Extended Data Fig. 3.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Li, X., Gao, B., Qin, Q. et al. Federated learning using a memristor compute-in-memory chip with in situ physical unclonable function and true random number generator. Nat Electron 8, 518–528 (2025). https://doi.org/10.1038/s41928-025-01390-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-025-01390-6